SL-ADP-PCIe-M2 Datasheet and Pinout

From SomLabs Wiki

SL-ADP-PCIe-M2 M.2 PCIe mass storage adapter Datasheet and Pinout

General description

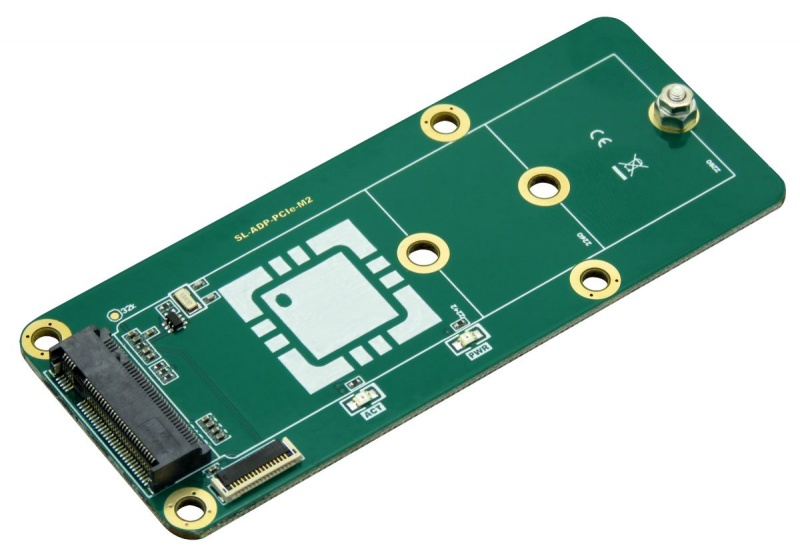

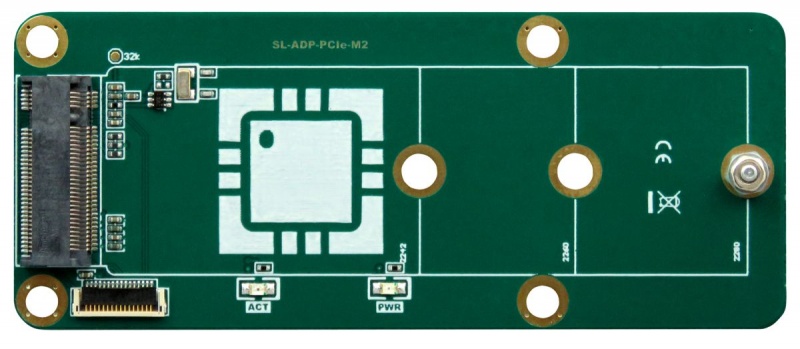

SL-ADP-PCIe-M2 is adapter dedicated to using M.2 mass storage (SSD, single lane) in embedded systems based on i.MX8Mmini MPU. The SL-ADP-PCIe-M2 module is equipped with M.2 key M connector and is compatible with 2242, 2260 or 2280 modules.

The SL-ADP-PCIe-M2 module is equipped with FPC16 connector - the same like in SoMLabs carrier board VisionCB-8M-STD.

Features

- Equipped with M.2 key M SSD socket

- Single rail +3.3V power supply

- Single lane PCIe communication interface

- Operating temperature -30÷+85°C

- Fully compatible with SoMLabs carrier boards equippped with PCIe interface on FPC16 connector

- Built-in 32kHz clock source

- Built-in two LEDs

- Compatible with 2242, 2260 and 2280 modules

- Connection with carrier board using FPC16 cable

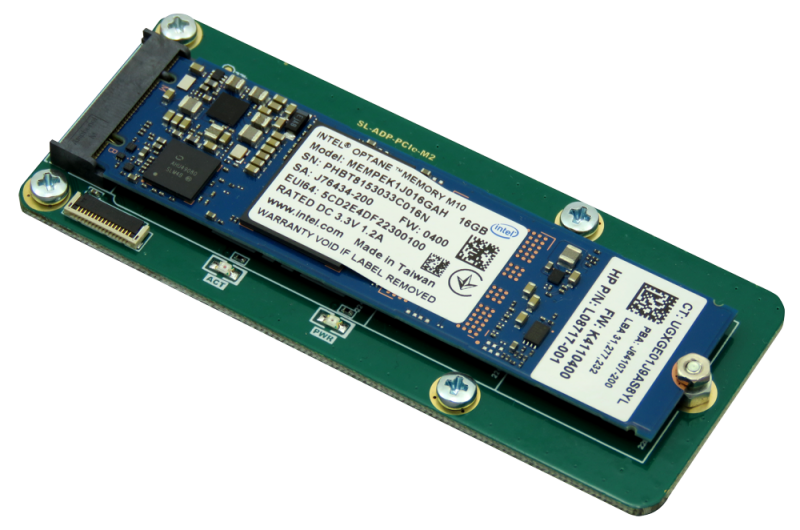

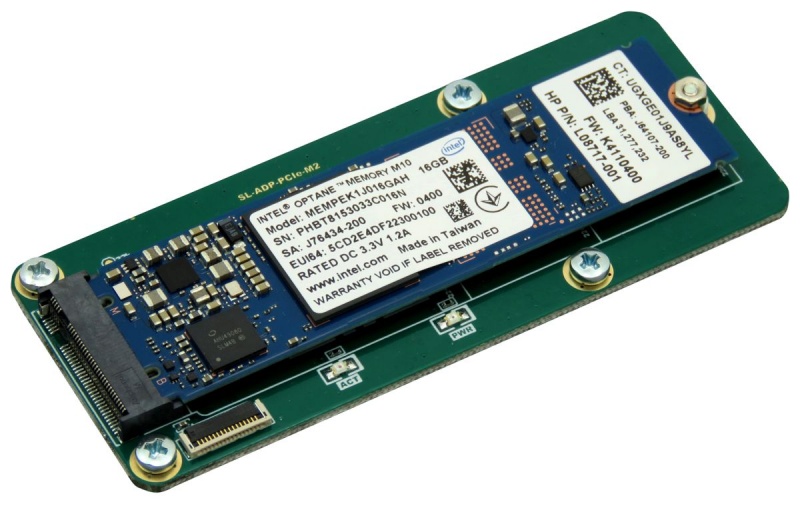

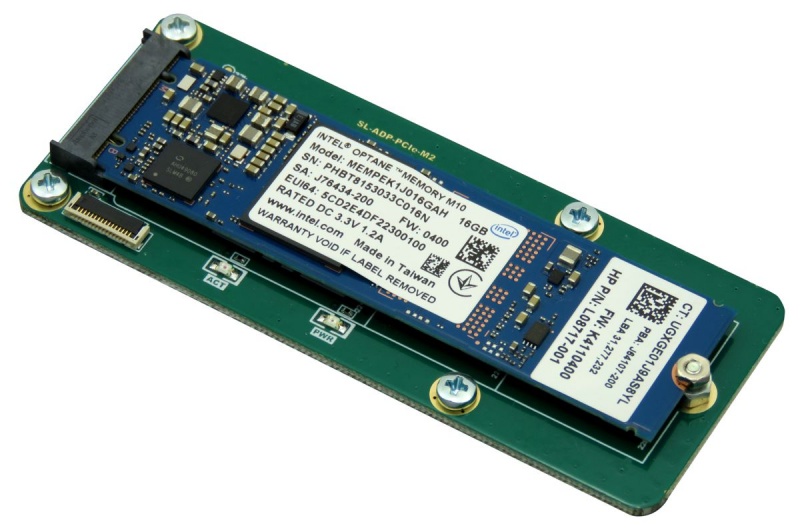

Pictures

Note: the SSD module shown in the picture is not included in the SL-ADP-PCIe-M2 kit!

Ordering info

SL-ADP-PCIe-M2 - FPC 16-pin flat cable (A-A) is included. The SSD module is not included in the SL-ADP-PCIe-M2 kit.

Operating ranges

| Parameter | Value | Unit | Comment |

|---|---|---|---|

| Power Supply | Powered from carrier board | ||

| Current | Maximum peak value (excluding SSD module) | ||

| Working temperature | oC | - |

Electrical parameters

| Signal name | Parameter | Value | Units | ||

|---|---|---|---|---|---|

| Min. | Typ. | Max. | |||

| +3.3V | Supply Voltage | 3.2 | 3.3 | 3.35 | V |

| I3.3V | Supply Current (3.3V) | 1 | - | 15 | mA |

| fSUSCLK | Suspend mode CLK frequency | - | 32 | - | kHz |

Note:

1. Current consumption value without SSD module.

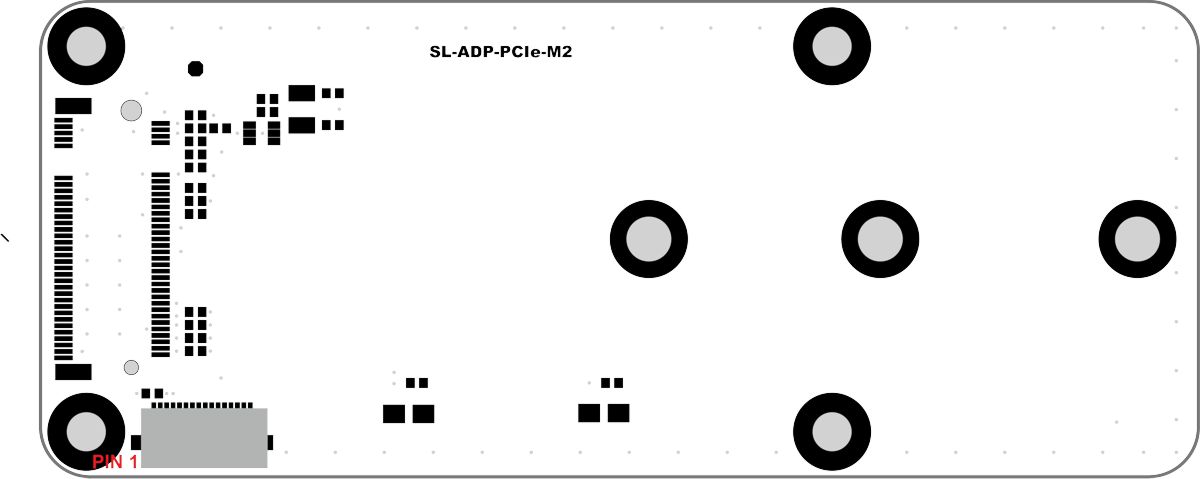

PCIe Pinout

| FPC16 connector pin | Function name | Description |

|---|---|---|

| 1 | - | - |

| 2 | - | - |

| 3 | +3.3V | Power supply |

| 4 | +3.3V | Power supply |

| 5 | - | - |

| 6 | - | - |

| 7 | GND | - |

| 8 | PCIe_CLK_n | Negative CLK data lane |

| 9 | PCIe_CLK_p | Positive CLK data lane |

| 10 | GND | - |

| 11 | PCIe_TXN_p | Positive TX data lane |

| 12 | PCIe_TXN_n | Negative TX data lane |

| 13 | GND | - |

| 14 | PCIe_RXN_p | Positive RX data lane |

| 15 | PCIe_RXN_n | Negative RX data lane |

| 16 | GND | - |

Note:

1. nPERST, nCLKREQ and nPEWAKE pins are connected to +3.3V with 10k pull-up resistors.

2. 32kHz generator connected to SUSCLK input.

3. ACT LED is controlled by DAS/DSS/nLED1 pin.

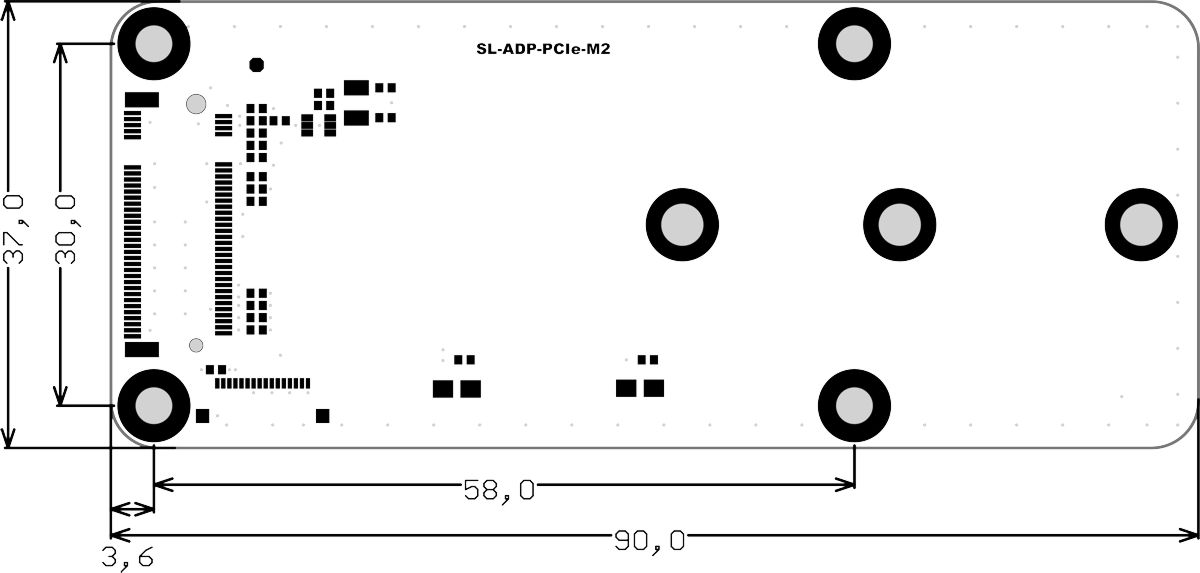

Dimensions