|

|

| (52 intermediate revisions by 3 users not shown) |

| Line 1: |

Line 1: |

| {{PageHeader|VisionSOM-6ULL Datasheet and Pinout}} __toc__ | | {{PageHeader|Display module SL-TFT7-TP-800-480 Datasheet and Pinout}} __toc__ |

| __jzpdf__ | | __jzpdf__ |

| == General description == | | == General description == |

| [[File:SL-TFT7-TP-800-480-front-rocks.png|800px|center]] | | [[File:SL-TFT7-TP-800-480-front-rocks.png|800px|center]] |

| <br> | | <br> |

| SL-TFT7-TP-800-480 is complete display TFT-LCD (800x480 px) module integrated with capactive touch-panel. Module is powered from +5V @400mA, data interface is 24 b parallel RGB + I2C (touch-panel controller). SL-TFT7-TP-800-480 module is equpiied with FPC50 connector, 1:1 compatible with SoMLabs carrier, eval and base boards. | | SL-TFT7-TP-800-480 is complete display TFT-LCD (800x480 pixels) module integrated with capactive touch-panel. Module is powered from +5V @400mA, data interface is 24-bit parallel RGB + I2C (for touch-panel controller). SL-TFT7-TP-800-480 module is equpiied with FPC50 connector, 1:1 compatible with VisionCB-STD v.1.0 and VisionCB-STD v.1.4. |

| SOMLabs also provides a complete hardware and software development board for the SoM in the form of a carrier board and optional TFT display and touch panel. | | SOMLabs also provides a complete hardware and software development board for the SoM in the form of a carrier board and optional TFT display and touch-panel. |

|

| |

|

| == Features == | | == Features == |

| * Powered by Powertip PH800480T013-IBC06 LCD-TFT | | * Powered by Powertip PH800480T013-IBC15 LCD-TFT |

| * Display size 7 inches | | * Display size 7 inches |

| * Display LCD matrix 800x480 px | | * Display LCD matrix 800x480 px |

| Line 15: |

Line 15: |

| * Single supply +5V (DC/DC converters built-in) | | * Single supply +5V (DC/DC converters built-in) |

| * Backlight LEDs built-in | | * Backlight LEDs built-in |

| * Fully compatible with SoMLabs carrier, eval and base boards | | * Compatible with SoMLabs carrier boards: |

| | ** VisionCB-STD v.1.0 |

| | ** VisionCB-STD v.1.4 |

|

| |

|

| == Pictures of SL-TFT7-TP-800-480 module == | | == Multimedia == |

| [[File:SL-TFT7-TP-800-480-back-shop.jpg]]<br>

| | |

| | {{#ev:youtube|NMKK1aid5M0|560x315|center}} |

| | <br> |

| | {{#ev:youtube|BeojPOAzAdU|560x315|center}} |

| | <br> |

| | {{#ev:youtube|oQTZ0I14acY|560x315|center}} |

| | |

| | == Pictures == |

| [[File:SL-TFT7-TP-800-480-front-empty-shop.jpg]]<br> | | [[File:SL-TFT7-TP-800-480-front-empty-shop.jpg]]<br> |

| [[File:SL-TFT7-TP-800-480-front-rocks-shop.jpg]]<br> | | [[File:SL-TFT7-TP-800-480-front-rocks-shop.jpg]]<br> |

| Line 25: |

Line 34: |

|

| |

|

| == Ordering info == | | == Ordering info == |

| '''SL-TFT7-TP-800-480''' | | '''SL-TFT7-TP-800-480''' - FPC 50-pin 15-cm flat cable (A-A) is included. |

| | |

| == Block Diagram ==

| |

| [[File:SL-TFT7-TP-800-480-blokowy.png|center]]

| |

|

| |

|

| == Operating ranges == | | == Operating ranges == |

| Line 55: |

Line 61: |

| | <center>max. 3.3</center> | | | <center>max. 3.3</center> |

| | <center>V</center> | | | <center>V</center> |

| | I2C interface, 2,2k pull-up resistor on SDA and SCL lines | | | I2C interface, 2.2kΩ pull-up resistor on SDA and SCL lines |

| |- | | |- |

| |Environment temperature | | |Environment temperature |

| Line 65: |

Line 71: |

| == Electrical parameters == | | == Electrical parameters == |

| {| class="wikitable" | | {| class="wikitable" |

| ! rowspan="2" | SOM<br />signal name | | ! rowspan="2" | Signal name |

| ! rowspan="2" | Parameter | | ! rowspan="2" | Parameter |

| ! colspan="3" | Value | | ! colspan="3" | Value |

| Line 95: |

Line 101: |

| | V | | | V |

| |- | | |- |

| | VTPIO | | | V<sub>TPIO</sub> |

| | TP controller IO Voltage | | | TP Controller IO Voltage |

| | 0 | | | 0 |

| | 3.3 | | | 3.3 |

| Line 102: |

Line 108: |

| | V | | | V |

| |- | | |- |

| | f<sub>I2C</sub> | | | V<sub>PWREN</sub> |

| | TP controller I2C speed | | | Power Enable Input Voltage |

| | | 0 |

| | | - |

| | | 5.5 |

| | | V |

| | |- |

| | | f<sub>TPI2C</sub> |

| | | TP Controller I2C Speed |

| | - | | | - |

| | - | | | - |

| Line 109: |

Line 122: |

| | kHz | | | kHz |

| |- | | |- |

| | VDD-COIN-3V | | | f<sub>PWM</sub> |

| | SNVS Backup<br />Battery Supply

| | | PWM Dimming Frequency |

| | 2.66 | |

| | - | | | - |

| | 3.6 | | | - |

| | V | | | 1 |

| | | kHz |

| | |- |

| | | R<sub>INT</sub> |

| | | Interrupt Output Pull-up Resistance |

| | | - |

| | | 10 |

| | | - |

| | | kΩ |

| | |- |

| | | R<sub>PWREN</sub> |

| | | Power Enable Pull-up Resistance |

| | | - |

| | | 10 |

| | | - |

| | | kΩ |

| |- | | |- |

| | | R<sub>TPI2C</sub> |

| | | Touch Panel Controller I2C IOs Pull-up Resistance |

| | - | | | - |

| | ADC Inputs Voltage | | | 2.2 |

| | 0

| |

| | - | | | - |

| | 3.3 | | | kΩ |

| | V

| |

| |} | | |} |

| Notes:<br />

| |

| 1. Excluding external load connected to +3.3VOUT lines.<br />

| |

|

| |

|

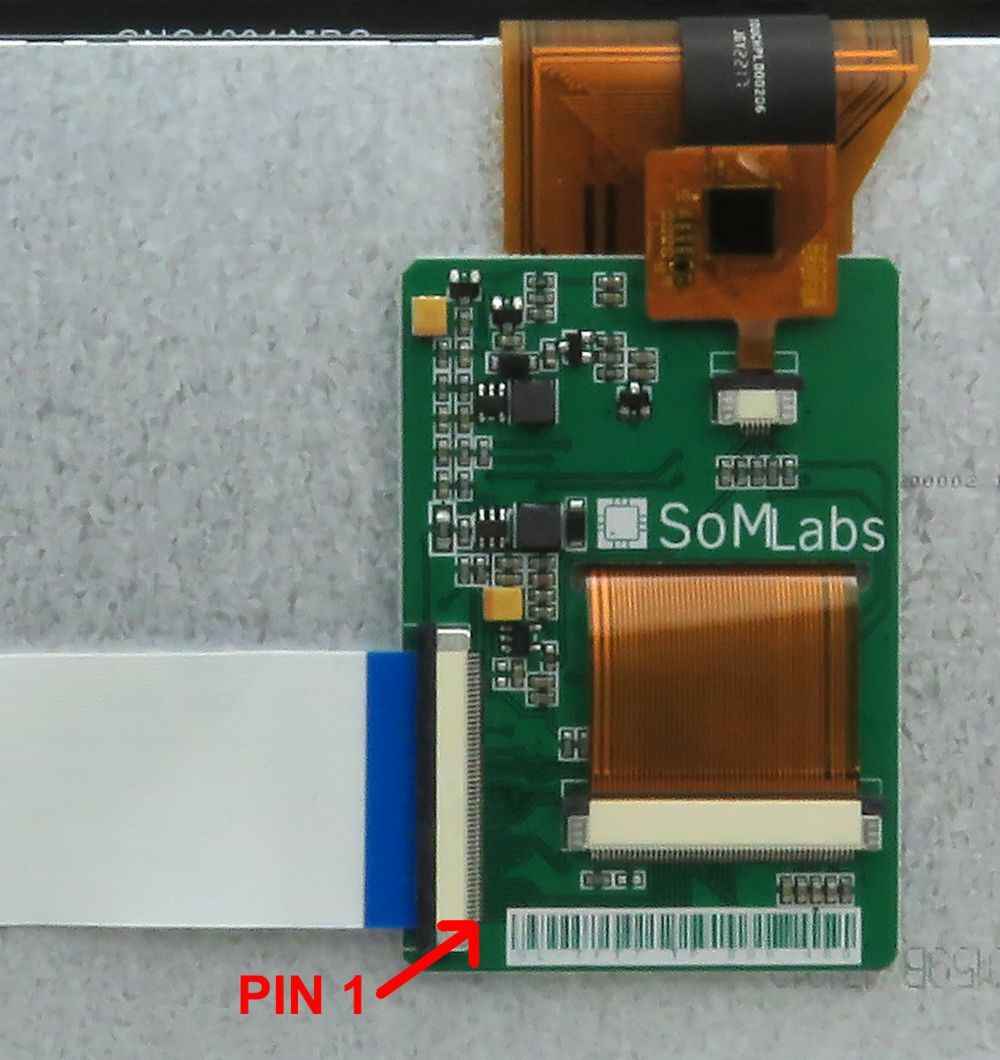

| == SOM pinout == | | == Pinout == |

| | [[File:Sl-tft7-tp-800-480-pin1.jpg]] |

| | <br /> |

| | <br> |

| {| class="wikitable" | | {| class="wikitable" |

| ! style="text-align: center; font-weight: bold;" | SODIMM PIN | | ! style="text-align: center; font-weight: bold;" | FPC50 connector pin |

| ! style="text-align: center; font-weight: bold;" | Functional

| |

| domain

| |

| ! style="text-align: center; font-weight: bold;" | Function name | | ! style="text-align: center; font-weight: bold;" | Function name |

| ! style="text-align: center; font-weight: bold;" | i.MX6 UltraLite/ | | ! style="text-align: center; font-weight: bold;" | Description |

| ULL Pad Name

| |

| ! style="text-align: center; font-weight: bold;" | Alternate functions

| |

| ! Description (refer to i.MX6 UltraLite/ULL manuals for details)

| |

| |- | | |- |

| | 1 | | | 1 |

| | Power | | | B0 |

| | GND | | | Blue 0 input |

| | -

| |

| | -

| |

| | -

| |

| |- | | |- |

| | 2 | | | 2 |

| | Power | | | B1 |

| | GND | | | Blue 1 input |

| | -

| |

| | -

| |

| | -

| |

| |- | | |- |

| | 3 | | | 3 |

| | Ctrl | | | B2 |

| | PMIC-STBY-REQ | | | Blue 2 input |

| | CCM_PMIC_STBY_REQ

| |

| | -

| |

| | Output, leave open if not used.

| |

| |- | | |- |

| | 4 | | | 4 |

| | Ctrl | | | B3 |

| | MX6-POR-B | | | Blue 3 input |

| | -

| |

| | -

| |

| | External warm reset input, active L.

| |

| |- | | |- |

| | 5 | | | 5 |

| | Ctrl | | | B4 |

| | PMIC-ON-REQ | | | Blue 4 input |

| | SNVS_PMIC_ON_REQ

| |

| | -

| |

| | Output, leave open if not used.

| |

| |- | | |- |

| | 6 | | | 6 |

| | Power | | | B5 |

| | VDD-SNVS-3V3 | | | Blue 5 input |

| | VDD_SNVS_IN

| |

| | -

| |

| | SNVS backup power supply must be held between 2.9V and 3.3V if the system requires keeping real time and other data on OFF state. Internally connected to +3.3V, leave open.

| |

| |- | | |- |

| | 7 | | | 7 |

| | BOOT | | | B6 |

| | BOOT-MODE1 | | | Blue 6 input |

| | BOOT_MODE1

| |

| | GPIO5_IO11

| |

| | BOOT-MODE1 BOOT-MODE0

| |

| | |

| 00 boot from fuses (default)

| |

| | |

| 01 serial downloader

| |

| | |

| 10 internal boot

| |

| | |

| 11 reserved

| |

| | |

| |- | | |- |

| | 8 | | | 8 |

| | Power | | | B7 |

| | VDD-COIN-3V | | | Blue 7 input |

| | VDD_SNVS_IN

| |

| | -

| |

| | Optional external coin battery for SNVS power domain, must be held between 2.9V and 3.3V if the system requires keeping real time and other data on OFF state.

| |

| Leave open if not used.

| |

| |- | | |- |

| | 9 | | | 9 |

| | BOOT | | | GND |

| | BOOT-MODE0 | | | Power supply |

| | BOOT_MODE0

| |

| | GPIO5_IO10

| |

| | BOOT-MODE1 BOOT-MODE0

| |

| | |

| 00 boot from fuses (default)

| |

| | |

| 01 serial downloader

| |

| | |

| 10 internal boot

| |

| | |

| 11 reserved

| |

| | |

| |- | | |- |

| | 10 | | | 10 |

| | GPIO-SNVS | | | G0 |

| | SNVS-TAMPER9 | | | Green 0 input |

| | SNVS_TAMPER9

| |

| | GPIO5_IO09

| |

| | Tamper input (SNVS power domain) or GPIO 3.3V.

| |

| |- | | |- |

| | 11 | | | 11 |

| | USB | | | G1 |

| | USB-OTG2-VBUS | | | Green 1 input |

| | USB_OTG2_VBUS

| |

| | -

| |

| | +5V USB bus. Leave open if not used.

| |

| |- | | |- |

| | 12 | | | 12 |

| | GPIO-SNVS | | | G2 |

| | SNVS-TAMPER5 | | | Green 2 input |

| | SNVS_TAMPER5

| |

| | GPIO5_IO05

| |

| | Tamper input (SNVS power domain) or GPIO 3.3V.

| |

| |- | | |- |

| | 13 | | | 13 |

| | USB | | | G3 |

| | USB-OTG1-VBUS | | | Green 3 input |

| | USB_OTG1_VBUS

| |

| | -

| |

| | +5V USB bus. Leave open if not used.

| |

| |- | | |- |

| | 14 | | | 14 |

| | Ctrl | | | G4 |

| | ONOFF | | | Green 4 input |

| | SRC_RESET_B

| |

| |

| |

| | Input for power interrupt generation. Leave open if not used.

| |

| |- | | |- |

| | 15 | | | 15 |

| | Power | | | G5 |

| | GND | | | Green 5 input |

| | -

| |

| | -

| |

| | -

| |

| |- | | |- |

| | 16 | | | 16 |

| | Ctrl | | | G6 |

| | POR-B | | | Green 6 input |

| | POR_B

| |

| | -

| |

| | Cold reset negative logic input resets all modules and logic in the IC.

| |

| May be used in addition to internally generated power on reset signal (logical AND, both internal and external signals are considered active low).

| |

| |- | | |- |

| | 17 | | | 17 |

| | Power | | | G7 |

| | GND | | | Green 7 input |

| | -

| |

| | -

| |

| | -

| |

| |- | | |- |

| | 18 | | | 18 |

| | GPIO-SNVS | | | GND |

| | SNVS-TAMPER8 | | | Power supply |

| | SNVS_TAMPER8

| |

| | GPIO5_IO08

| |

| | Tamper input (SNVS power domain) or GPIO 3.3V.

| |

| |- | | |- |

| | 19 | | | 19 |

| | USB | | | R0 |

| | USB-OTG2-DP | | | Red 0 input |

| | USB_OTG2_DP

| |

| | -

| |

| | Leave open if not used.

| |

| |- | | |- |

| | 20 | | | 20 |

| | Power | | | R1 |

| | GND | | | Red 1 input |

| | -

| |

| | -

| |

| | -

| |

| |- | | |- |

| | 21 | | | 21 |

| | USB | | | R2 |

| | USB-OTG2-DN | | | Red 2 input |

| | USB_OTG2_DN

| |

| | -

| |

| | Leave open if not used.

| |

| |- | | |- |

| | 22 | | | 22 |

| | Power | | | R3 |

| | GND | | | Red 3 input |

| | -

| |

| | -

| |

| | -

| |

| |- | | |- |

| | 23 | | | 23 |

| | Power | | | R4 |

| | GND | | | Red 4 input |

| | -

| |

| | -

| |

| | -

| |

| |- | | |- |

| | 24 | | | 24 |

| | GPIO-SNVS | | | R5 |

| | SNVS-TAMPER7 | | | Red 5 input |

| | SNVS_TAMPER7

| |

| | GPIO5_IO07

| |

| | Tamper input (SNVS power domain) or GPIO 3.3V.

| |

| |- | | |- |

| | 25 | | | 25 |

| | USB | | | R6 |

| | USB-OTG1-DP | | | Red 6 input |

| | USB_OTG1_DP

| |

| | -

| |

| | Leave open if not used.

| |

| |- | | |- |

| | 26 | | | 26 |

| | Power | | | R7 |

| | GND | | | Red 7 input |

| | -

| |

| | -

| |

| | -

| |

| |- | | |- |

| | 27 | | | 27 |

| | USB | | | GND |

| | USB-OTG1-DN | | | Power supply |

| | USB_OTG1_DN

| |

| | -

| |

| | Leave open if not used.

| |

| |- | | |- |

| | 28 | | | 28 |

| | Power | | | DE |

| | GND | | | DE display controller input |

| | -

| |

| | -

| |

| | -

| |

| |- | | |- |

| | 29 | | | 29 |

| | Power | | | HSYNC |

| | GND | | | HSYNC display controller input |

| | -

| |

| | -

| |

| | -

| |

| |- | | |- |

| | 30 | | | 30 |

| | GPIO-SNVS | | | VSYNC |

| | SNVS-TAMPER4 | | | VSYNC display controller input |

| | SNVS_TAMPER4

| |

| | GPIO5_IO04

| |

| | Tamper input (SNVS power domain) or GPIO 3.3V.

| |

| |- | | |- |

| | 31 | | | 31 |

| | USB | | | GND |

| | nUSB-OTG-CHD | | | Power supply |

| | USB_OTG1_CHD_B

| |

| | -

| |

| | Leave open if not used.

| |

| |- | | |- |

| | 32 | | | 32 |

| | GPIO-SNVS | | | DCLK |

| | SNVS-TAMPER1 | | | Main clock input (display controller) |

| | SNVS_TAMPER1

| |

| | GPIO5_IO01

| |

| | Tamper input (SNVS power domain) or GPIO 3.3V.

| |

| |- | | |- |

| | 33 | | | 33 |

| | JTAG | | | GND |

| | JTAG-MOD | | | Power supply |

| | JTAG_MOD

| |

| | -

| |

| | Leave open if not used.

| |

| |- | | |- |

| | 34 | | | 34 |

| | GPIO-SNVS | | | - |

| | SNVS-TAMPER3 | | | - |

| | SNVS_TAMPER3

| |

| | GPIO5_IO03

| |

| | Tamper input (SNVS power domain) or GPIO 3.3V.

| |

| |- | | |- |

| | 35 | | | 35 |

| | Power

| |

| | GND

| |

| | -

| |

| | - | | | - |

| | - | | | - |

| |- | | |- |

| | 36 | | | 36 |

| | GPIO-SNVS | | | nINT |

| | SNVS-TAMPER0 | | | Touch-panel controller interrupt output (OC with 10kΩ pull-up) |

| | SNVS_TAMPER0

| |

| | GPIO5_IO00

| |

| | Tamper input (SNVS power domain) or GPIO 3.3V.

| |

| |- | | |- |

| | 37 | | | 37 |

| | | | | GPIO1 |

| | CLK1-N | | | PWM signal input for backlight control (leave open if not used) |

| | CCM_CLK1_N

| |

| | -

| |

| | General purpose differential high speed clock input/output.

| |

| Leave open if not used.

| |

| |- | | |- |

| | 38 | | | 38 |

| | Power

| |

| | GND

| |

| | -

| |

| | - | | | - |

| | - | | | - |

| |- | | |- |

| | 39 | | | 39 |

| |

| |

| | CLK1-P

| |

| | CCM_CLK1_P

| |

| | - | | | - |

| | General purpose differential high speed clock input/output. | | | - |

| Leave open if not used.

| |

| |- | | |- |

| | 40 | | | 40 |

| | Power

| |

| | GND

| |

| | -

| |

| | - | | | - |

| | - | | | - |

| |- | | |- |

| | 41 | | | 41 |

| | Power

| |

| | GND

| |

| | -

| |

| | - | | | - |

| | - | | | - |

| |- | | |- |

| | 42 | | | 42 |

| | GPIO-SNVS | | | SCL |

| | SNVS-TAMPER6 | | | Touch-panel controller SCL input (with 2.2kΩ pull-up) |

| | SNVS_TAMPER6

| |

| | GPIO5_IO06

| |

| | Tamper input (SNVS power domain) or GPIO 3.3V.

| |

| |- | | |- |

| | 43 | | | 43 |

| | JTAG | | | SDA |

| | JTAG-TDI | | | Touch-panel controller SDA IO (with 2.2kΩ pull-up) |

| | JTAG_TDI

| |

| | -

| |

| | JTAG TDI input line.

| |

| |- | | |- |

| | 44 | | | 44 |

| | GPIO-SNVS | | | GND |

| | SNVS-TAMPER2 | | | Power supply |

| | SNVS_TAMPER2

| |

| | GPIO5_IO02

| |

| | Tamper input (SNVS power domain) or GPIO 3.3V.

| |

| |- | | |- |

| | 45 | | | 45 |

| | GPIO | | | NC |

| | GPIO-8 | | | No external connections! |

| | GPIO1_IO08

| |

| | PWM1_OUT

| |

| | |

| WDOG1_WDOG_B

| |

| | |

| SPDIF_OUT

| |

| | |

| CSI_VSYNC

| |

| | |

| USDHC2_VSELECT

| |

| | |

| CCM_PMIC_RDY

| |

| | |

| UART5_RTS_B

| |

| | |

| | Universal GPIO with 3.3V logic levels.

| |

| |- | | |- |

| | 46 | | | 46 |

| | JTAG | | | NC |

| | JTAG-TMS | | | No external connections! |

| | JTAG_TMS

| |

| | -

| |

| | JTAG TMS input line.

| |

| |- | | |- |

| | 47 | | | 47 |

| | GPIO | | | +5V |

| | GPIO-4 | | | Power supply |

| | GPIO1_IO04

| |

| | ENET1_REF_CLK1

| |

| | |

| PWM3_OUT

| |

| | |

| USB_OTG1_PWR

| |

| | |

| USDHC1_RESET_B

| |

| | |

| ENET2_1588_EVENT0_IN

| |

| | |

| UART5_TX

| |

| | |

| | Universal GPIO with 3.3V logic levels.

| |

| |- | | |- |

| | 48 | | | 48 |

| | JTAG | | | +5V |

| | JTAG-nTRST | | | Power supply |

| | JTAG_TRST_B

| |

| | -

| |

| | JTAG TRST input line (active L).

| |

| |- | | |- |

| | 49 | | | 49 |

| | GPIO | | | nRES_TP |

| | GPIO-5 | | | Touch-panel controller reset signal |

| | GPIO1_IO05

| |

| | ENET2_REF_CLK2

| |

| | |

| PWM4_OUT

| |

| | |

| ANATOP_OTG2_ID

| |

| | |

| CSI_FIELD

| |

| | |

| USDHC1_VSELECT

| |

| | |

| ENET2_1588_EVENT0_OUT

| |

| | |

| UART5_RX

| |

| | |

| | Universal GPIO with 3.3V logic levels.

| |

| WLAN-ENABLE in SOM with WiFi/BT module

| |

| |- | | |- |

| | 50 | | | 50 |

| | Power | | | PWREN |

| | GND | | | Backlight LEDs on/off, with 10kΩ pull-up resisitor (level +5V).<br />If PWREN pin is open or connected to "1" - LEDs are on. |

| | -

| | |} |

| | -

| |

| | -

| |

| |-

| |

| | 51

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 52

| |

| | JTAG

| |

| | JTAG-TDO

| |

| | JTAG_TDO

| |

| | -

| |

| | JTAG TDO output line.

| |

| |-

| |

| | 53

| |

| | GPIO

| |

| | GPIO-7

| |

| | GPIO1_IO07

| |

| | NET1_MDC

| |

| | |

| ENET2_MDC

| |

| | |

| USB_OTG_HOST_MODE

| |

| | |

| CSI_PIXCLK

| |

| | |

| USDHC2_CD_BCCM_STOP

| |

| | |

| UART1_RTS_B

| |

| | |

| | Universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 54

| |

| | JTAG

| |

| | JTAG-TCK

| |

| | JTAG_TCK

| |

| | -

| |

| | JTAG TCK input line.

| |

| Connected to JTAG-TCK line (via separating resistor 10k).

| |

| |-

| |

| | 55

| |

| | GPIO

| |

| | GPIO-3

| |

| | GPIO1_IO03

| |

| | I2C1_SDA

| |

| | |

| GPT1_COMPARE3

| |

| | |

| USB_OTG2_OC

| |

| | |

| USDHC1_CD_B

| |

| | |

| CCM_DI0_EXT_CLK

| |

| | |

| SRC_TESTER_ACK

| |

| | |

| | Universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 56

| |

| | GPIO

| |

| | GPIO-9

| |

| | GPIO1_IO09

| |

| | PWM2_OUT

| |

| | |

| WDOG1_WDOG_ANY

| |

| | |

| SPDIF_IN

| |

| | |

| CSI_HSYNC

| |

| | |

| USDHC2_RESET_B

| |

| | |

| USDHC1_RESET_B

| |

| | |

| UART5_CTS_B

| |

| | |

| | Universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 57

| |

| | COM-GPIO

| |

| | UART1-TXD

| |

| | UART1_TX_DATA

| |

| | ENET1_RDATA02

| |

| | |

| I2C3_SCL

| |

| | |

| CSI_DATA02

| |

| | |

| GPT1_COMPARE1

| |

| | |

| GPIO1_IO16

| |

| | |

| SPDIF_OUT

| |

| | |

| UART5_TX

| |

| | |

| | Default: UART1 TxD output or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 58

| |

| | GPIO

| |

| | GPIO-2

| |

| | GPIO1_IO02

| |

| | I2C1_SCL

| |

| | |

| GPT1_COMPARE2

| |

| | |

| USB_OTG2_PWR

| |

| | |

| ENET1_REF_CLK_25M

| |

| | |

| USDHC1_WPS

| |

| | |

| DMA_EXT_EVENT00

| |

| | |

| SRC_ANY_PU_RESET

| |

| | |

| UART1_TX

| |

| | |

| | Universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 59

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 60

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 61

| |

| | GPIO

| |

| | GPIO-6

| |

| | GPIO1_IO06

| |

| | ENET1_MDIO

| |

| | |

| ENET2_MDIO

| |

| | |

| USB_OTG_PWR_WAKE

| |

| | |

| CSI_MCLK

| |

| | |

| USDHC2_WPCCM_WAIT

| |

| | |

| CCM_REF_EN_B

| |

| | |

| UART1_CTS_B

| |

| | |

| | Universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 62

| |

| | GPIO

| |

| | GPIO-1

| |

| | GPIO1_IO01

| |

| | I2C2_SDA

| |

| | |

| GPT1_COMPARE1

| |

| | |

| USB_OTG1_OC

| |

| | |

| ENET2_REF_CLK2

| |

| | |

| MQS_LEFT

| |

| | |

| ENET1_1588_EVENT0_OUT

| |

| | |

| SRC_EARLY_RESET

| |

| | |

| WDOG1_WDOG_B

| |

| | |

| | Universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 63

| |

| | COM-GPIO

| |

| | UART1-RXD

| |

| | UART1_RX_DATA

| |

| | ENET1_RDATA03

| |

| | |

| I2C3_SDA

| |

| | |

| CSI_DATA03

| |

| | |

| GPT1_CLK

| |

| | |

| GPIO1_IO17

| |

| | |

| SPDIF_IN

| |

| | |

| UART5_RX

| |

| | |

| | Default: UART1 RxD input or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 64

| |

| | GPIO

| |

| | GPIO-0

| |

| | GPIO1_IO00

| |

| | I2C2_SCL

| |

| | |

| GPT1_CAPTURE1

| |

| | |

| ANATOP_OTG1_ID

| |

| | |

| ENET1_REF_CLK1

| |

| | |

| MQS_RIGHT

| |

| | |

| ENET1_1588_EVENT0_IN

| |

| | |

| SRC_SYSTEM_RESET

| |

| | |

| WDOG3_WDOG_B

| |

| | |

| | Universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 65

| |

| | COM-GPIO

| |

| | UART2-TXD

| |

| | UART2_TX_DATA

| |

| | ENET1_TDATA02

| |

| | |

| I2C4_SCL

| |

| | |

| CSI_DATA06

| |

| | |

| GPT1_CAPTURE1

| |

| | |

| GPIO1_IO20

| |

| | |

| ECSPI3_SS0

| |

| | |

| | Default: UART2 TxD output or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 66

| |

| | COM-GPIO

| |

| | UART1-CTS

| |

| | UART1_CTS_B

| |

| | ENET1_RX_CLK

| |

| | |

| USDHC1_WP

| |

| | |

| CSI_DATA04

| |

| | |

| ENET2_1588_EVENT1_IN

| |

| | |

| GPIO1_IO18

| |

| | |

| USDHC2_WP

| |

| | |

| UART5_CTS_B

| |

| | |

| | Default: UART1 CTS output or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 67

| |

| | COM-GPIO

| |

| | UART2-RXD

| |

| | UART2_RX_DATA

| |

| | ENET1_TDATA03

| |

| | |

| I2C4_SDA

| |

| | |

| CSI_DATA07

| |

| | |

| GPT1_CAPTURE2

| |

| | |

| GPIO1_IO21

| |

| | |

| SJC_DONE

| |

| | |

| ECSPI3_SCLK

| |

| | |

| | Default: UART2 RxD input or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 68

| |

| | COM-GPIO

| |

| | UART5-RXD

| |

| | UART5_RX_DATA

| |

| | ENET2_COL

| |

| | |

| I2C2_SDA

| |

| | |

| CSI_DATA15

| |

| | |

| CSU_CSU_INT_DEB

| |

| | |

| GPIO1_IO31

| |

| | |

| ECSPI2_MISO

| |

| | |

| EPDC_PWRCTRL03

| |

| | |

| | Default: UART5 RxD input or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 69

| |

| | COM-GPIO

| |

| | UART3-TXD

| |

| | UART3_TX_DATA

| |

| | ENET2_RDATA02

| |

| | |

| CSI_DATA01

| |

| | |

| UART2_CTS_B

| |

| | |

| GPIO1_IO24

| |

| | |

| SJC_JTAG_ACT

| |

| | |

| | Default: UART3 TxD input or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 70

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 71

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 72

| |

| | COM-GPIO

| |

| | UART2-CTS

| |

| | UART2_CTS_B

| |

| | ENET1_CRS

| |

| | |

| FLEXCAN2_TXCSI_DATA08

| |

| | |

| GPT1_COMPARE2

| |

| | |

| GPIO1_IO22

| |

| | |

| SJC_DE_B

| |

| | |

| ECSPI3_MOSI

| |

| | |

| | Default: UART2 CTS output or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 73

| |

| | COM-GPIO

| |

| | UART3-RXD

| |

| | UART3_RX_DATA

| |

| | ENET2_RDATA03

| |

| | |

| CSI_DATA00

| |

| | |

| UART2_RTS_B

| |

| | |

| GPIO1_IO25

| |

| | |

| EPIT1_OUT

| |

| | |

| | Default: UART3 RxD input or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 74

| |

| | COM-GPIO

| |

| | UART1-RTS

| |

| | UART1_RTS_B

| |

| | ENET1_TX_ER

| |

| | |

| USDHC1_CD_BCSI_DATA05

| |

| | |

| ENET2_1588_EVENT1_OUT

| |

| | |

| GPIO1_IO19

| |

| | |

| USDHC2_CD_B

| |

| | |

| UART5_RTS_B

| |

| | |

| | Default: UART1 RTS input or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 75

| |

| | COM-GPIO

| |

| | UART4-TXD

| |

| | UART4_TX_DATA

| |

| | ENET2_TDATA02

| |

| | |

| I2C1_SCL

| |

| | |

| CSI_DATA12

| |

| | |

| CSU_CSU_ALARM_AUT02

| |

| | |

| GPIO1_IO28

| |

| | |

| ECSPI2_SCLK

| |

| | |

| | Default: UART4 TxD output or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 76

| |

| | COM-GPIO

| |

| | UART3-CTS

| |

| | UART3_CTS_B

| |

| | ENET2_RX_CLK

| |

| | |

| FLEXCAN1_TX

| |

| | |

| CSI_DATA10

| |

| | |

| ENET1_1588_EVENT1_IN

| |

| | |

| GPIO1_IO26

| |

| | |

| EPIT2_OUT

| |

| | |

| | Default: UART3 CTS output or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 77

| |

| | COM-GPIO

| |

| | UART4-RXD

| |

| | UART4_RX_DATA

| |

| | ENET2_TDATA03

| |

| | |

| I2C1_SDA

| |

| | |

| CSI_DATA13

| |

| | |

| CSU_CSU_ALARM_AUT01

| |

| | |

| GPIO1_IO29

| |

| | |

| ECSPI2_SS0

| |

| | |

| EPDC_PWRCTRL01

| |

| | |

| | Default: UART4 RxD input or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 78

| |

| | COM-GPIO

| |

| | UART2-RTS

| |

| | UART2_RTS_B

| |

| | ENET1_COL

| |

| | |

| FLEXCAN2_RX

| |

| | |

| CSI_DATA09

| |

| | |

| GPT1_COMPARE3

| |

| | |

| GPIO1_IO23

| |

| | |

| SJC_FAIL

| |

| | |

| ECSPI3_MISO

| |

| | |

| | Default: UART2 RTS input or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 79

| |

| | COM-GPIO

| |

| | UART5-TXD

| |

| | UART5_TX_DATA

| |

| | GPIO1_IO30

| |

| | |

| ECSPI2_MOSI

| |

| | |

| EPDC_PWRCTRL02

| |

| | |

| ENET2_CRS

| |

| | |

| I2C2_SCL

| |

| | |

| CSI_DATA14

| |

| | |

| CSU_CSU_ALARM_AUT00

| |

| | |

| | Default: UART5 TxD output or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 80

| |

| | COM-GPIO

| |

| | UART3-RTS

| |

| | UART3_RTS_B

| |

| | ENET2_TX_ER

| |

| | |

| FLEXCAN1_RX

| |

| | |

| CSI_DATA11

| |

| | |

| ENET1_1588_EVENT1_OUT

| |

| | |

| GPIO1_IO27

| |

| | |

| WDOG1_WDOG_B

| |

| | |

| | Default: UART3 RTS input or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 81

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 82

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 83

| |

| | NC

| |

| | -

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 84

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 85

| |

| | Power

| |

| | +3.3VOUT

| |

| | -

| |

| | -

| |

| | +3.3V generated by SOM's LDO.

| |

| |-

| |

| | 86

| |

| | NC

| |

| | -

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 87

| |

| | Power

| |

| | +3.3VOUT

| |

| | -

| |

| | -

| |

| | +3.3V generated by SOM's LDO.

| |

| |-

| |

| | 88

| |

| | Power

| |

| | +3.3VOUT

| |

| | -

| |

| | -

| |

| | +3.3V generated by SOM's LDO.

| |

| |-

| |

| | 89

| |

| | Power

| |

| | +3.3VOUT

| |

| | -

| |

| | -

| |

| | +3.3V generated by SOM's LDO.

| |

| |-

| |

| | 90

| |

| | Power

| |

| | +3.3VOUT

| |

| | -

| |

| | -

| |

| | +3.3V generated by SOM's LDO.

| |

| |-

| |

| | 91

| |

| | Power

| |

| | +3.3VOUT

| |

| | -

| |

| | -

| |

| | +3.3V generated by SOM's LDO.

| |

| |-

| |

| | 92

| |

| | Power

| |

| | +3.3VOUT

| |

| | -

| |

| | -

| |

| | +3.3V generated by SOM's LDO.

| |

| |-

| |

| | 93

| |

| | Power

| |

| | +3.3VOUT

| |

| | -

| |

| | -

| |

| | +3.3V generated by SOM's LDO.

| |

| |-

| |

| | 94

| |

| | NC

| |

| | -

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 95

| |

| | NC

| |

| | -

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 96

| |

| | Power

| |

| | +5VIN

| |

| | -

| |

| | -

| |

| | +4.0-5.5V input power supply.

| |

| |-

| |

| | 97

| |

| | Ethernet

| |

| | ENET1-RXD0

| |

| | ENET1_RX_DATA0

| |

| | UART4_RTS_B

| |

| | |

| PWM1_OUT

| |

| | |

| CSI_DATA16

| |

| | |

| FLEXCAN1_TX

| |

| | |

| GPIO2_IO00

| |

| | |

| KPP_ROW00

| |

| | |

| USDHC1_LCTL

| |

| | |

| EPDC_SDCE04

| |

| | |

| | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 98

| |

| | Power

| |

| | +5VIN

| |

| | -

| |

| | -

| |

| | +4.0-5.5V input power supply.

| |

| |-

| |

| | 99

| |

| | Ethernet

| |

| | ENET1-RXD1

| |

| | ENET1_RX_DATA1

| |

| | UART4_CTS_B

| |

| | |

| PWM2_OUT

| |

| | |

| CSI_DATA17

| |

| | |

| FLEXCAN1_RX

| |

| | |

| GPIO2_IO01

| |

| | |

| KPP_COL00

| |

| | |

| USDHC2_LCTL

| |

| | |

| EPDC_SDCE05

| |

| | |

| | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 100

| |

| | Power

| |

| | +5VIN

| |

| | -

| |

| | -

| |

| | +4.0-5.5V input power supply.

| |

| |-

| |

| | 101

| |

| | Ethernet

| |

| | ENET1-CRS-DV

| |

| | ENET1_RX_EN

| |

| | UART5_RTS_B

| |

| | |

| CSI_DATA18

| |

| | |

| FLEXCAN2_TX

| |

| | |

| GPIO2_IO02

| |

| | |

| KPP_ROW01

| |

| | |

| USDHC1_VSELECT

| |

| | |

| EPDC_SDCE06

| |

| | |

| | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 102

| |

| | Power

| |

| | +5VIN

| |

| |

| |

| |

| |

| | +4.0-5.5V input power supply.

| |

| |-

| |

| | 103

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 104

| |

| | Power

| |

| | +5VIN

| |

| |

| |

| |

| |

| | +4.0-5.5V input power supply.

| |

| |-

| |

| | 105

| |

| | Ethernet

| |

| | ENET2-TX-CLK

| |

| | ENET2_TX_CLK

| |

| | UART8_CTS_B

| |

| | |

| ECSPI4_MISO

| |

| | |

| ENET2_REF_CLK2

| |

| | |

| GPIO2_IO14

| |

| | |

| KPP_ROW07

| |

| | |

| ANATOP_OTG2_ID

| |

| | |

| EPDC_SDDO14

| |

| | |

| | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| 10R resistor connected in series.

| |

| |-

| |

| | 106

| |

| | Power

| |

| | +5VIN

| |

| |

| |

| |

| |

| | +4.0-5.5V input power supply.

| |

| |-

| |

| | 107

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 108

| |

| | Power

| |

| | +5VIN

| |

| |

| |

| |

| |

| | +4.0-5.5V input power supply.

| |

| |-

| |

| | 109

| |

| | Ethernet

| |

| | ENET2-RXER

| |

| | ENET2_RX_ER

| |

| | UART8_RTS_B

| |

| | |

| ECSPI4_SS0

| |

| | |

| EIM_ADDR25

| |

| | |

| GPIO2_IO15

| |

| | |

| KPP_COL07

| |

| | |

| WDOG1_WDOG_ANY

| |

| | |

| EPDC_SDDO15

| |

| | |

| | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| Connected to WD_G-B line.

| |

| |-

| |

| | 110

| |

| | Power

| |

| | +5VIN

| |

| | -

| |

| | -

| |

| | +4.0-5.5V input power supply.

| |

| |-

| |

| | 111

| |

| | Ethernet

| |

| | ENET2-RXD0

| |

| | ENET2_RX_DATA0

| |

| | UART6_TX

| |

| | |

| I2C3_SCL

| |

| | |

| ENET1_MDIO

| |

| | |

| GPIO2_IO08

| |

| | |

| KPP_ROW04

| |

| | |

| USB_OTG1_PWR

| |

| | |

| EPDC_SDDO08

| |

| | |

| | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 112

| |

| | Power

| |

| | +5VIN

| |

| | -

| |

| | -

| |

| | +4.0-5.5V input power supply.

| |

| |-

| |

| | 113

| |

| | Ethernet

| |

| | ENET2-RXD1

| |

| | ENET2_RX_DATA1

| |

| | UART6_RX

| |

| | |

| I2C3_SDA

| |

| | |

| ENET1_MDC

| |

| | |

| GPIO2_IO09

| |

| | |

| KPP_COL04

| |

| | |

| USB_OTG1_OCE

| |

| | |

| PDC_SDDO09

| |

| | |

| | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 114

| |

| | Ethernet

| |

| | ENET1-TXEN

| |

| | ENET1_TX_EN

| |

| | UART6_RTS_B

| |

| | |

| PWM6_OUT

| |

| | |

| CSI_DATA21

| |

| | |

| ENET2_MDC

| |

| | |

| GPIO2_IO05

| |

| | |

| KPP_COL02

| |

| | |

| WDOG2_WDOG_RST_B_DEB

| |

| | |

| EPDC_SDCE09

| |

| | |

| | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 115

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 116

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 117

| |

| | Ethernet

| |

| | ENET2-CRS-DV

| |

| | ENET2_RX_EN

| |

| | UART7_TX

| |

| | |

| I2C4_SCL

| |

| | |

| EIM_ADDR26

| |

| | |

| GPIO2_IO10

| |

| | |

| KPP_ROW05

| |

| | |

| ENET1_REF_CLK_25M

| |

| | |

| EPDC_SDDO10

| |

| | |

| | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 118

| |

| | Ethernet

| |

| | ENET1-TX-CLK

| |

| | ENET1_TX_CLK

| |

| | UART7_CTS_B

| |

| | |

| PWM7_OUT

| |

| | |

| CSI_DATA22

| |

| | |

| ENET1_REF_CLK1

| |

| | |

| GPIO2_IO06

| |

| | |

| KPP_ROW03

| |

| | |

| GPT1_CLK

| |

| | |

| EPDC_SDOED

| |

| | |

| | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| 10R resistor connected in series.

| |

| |-

| |

| | 119

| |

| | Ethernet

| |

| | ENET2-TXD1

| |

| | ENET2_TX_DATA1

| |

| | UART8_TX

| |

| | |

| ECSPI4_SCLK

| |

| | |

| EIM_EB_B03

| |

| | |

| GPIO2_IO12

| |

| | |

| KPP_ROW06

| |

| | |

| USB_OTG2_PWR

| |

| | |

| EPDC_SDDO12

| |

| | |

| | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 120

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 121

| |

| | Ethernet

| |

| | ENET2-TXEN

| |

| | ENET2_TX_EN

| |

| | UART8_RX

| |

| | |

| ECSPI4_MOSI

| |

| | |

| EIM_ACLK_FREERUN

| |

| | |

| GPIO2_IO13

| |

| | |

| KPP_COL06

| |

| | |

| USB_OTG2_OC

| |

| | |

| EPDC_SDDO13

| |

| | |

| |

| |

| |-

| |

| | 122

| |

| | Ethernet

| |

| | ENET1-TXD0

| |

| | ENET1_TX_DATA0

| |

| | UART5_CTS_B

| |

| | |

| CSI_DATA19

| |

| | |

| FLEXCAN2_RX

| |

| | |

| GPIO2_IO03

| |

| | |

| KPP_COL01

| |

| | |

| USDHC2_VSELECT

| |

| | |

| EPDC_SDCE07

| |

| | |

| | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |- | |

| | 123

| |

| | Ethernet

| |

| | ENET2-TXD0

| |

| | ENET2_TX_DATA0

| |

| | UART7_RX

| |

| | |

| I2C4_SDA

| |

| | |

| EIM_EB_B02

| |

| | |

| GPIO2_IO11

| |

| | |

| KPP_COL05

| |

| | |

| EPDC_SDDO11

| |

| | |

| | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 124

| |

| | Ethernet

| |

| | ENET1-TXD1

| |

| | ENET1_TX_DATA1

| |

| | UART6_CTS_B

| |

| | |

| PWM5_OUT

| |

| | |

| CSI_DATA20

| |

| | |

| ENET2_MDIO

| |

| | |

| GPIO2_IO04

| |

| | |

| KPP_ROW02

| |

| | |

| WDOG1_WDOG_RST_B_DEB

| |

| | |

| EPDC_SDCE08

| |

| | |

| | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 125

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 126

| |

| | Ethernet

| |

| | ENET1-RXER

| |

| | ENET1_RX_ER

| |

| | UART7_RTS_B

| |

| | |

| PWM8_OUT

| |

| | |

| CSI_DATA23

| |

| | |

| EIM_CRE

| |

| | |

| GPIO2_IO07

| |

| | |

| KPP_COL03

| |

| | |

| GPT1_CAPTURE2

| |

| | |

| EPDC_SDOEZ

| |

| | |

| | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 127

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 128

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 129

| |

| | LCD

| |

| | LCD-DATA21

| |

| | LCD_DATA21

| |

| | UART8_RX

| |

| | |

| ECSPI1_SS0

| |

| | |

| CSI_DATA13

| |

| | |

| EIM_DATA13

| |

| | |

| GPIO3_IO26

| |

| | |

| SRC_BT_CFG29

| |

| | |

| USDHC2_DATA1

| |

| | |

| EPDC_SDCE01

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 130

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 131

| |

| | LCD

| |

| | LCD-DATA22

| |

| | LCD_DATA22

| |

| | MQS_RIGHT

| |

| | |

| ECSPI1_MOSI

| |

| | |

| CSI_DATA14

| |

| | |

| EIM_DATA14

| |

| | |

| GPIO3_IO27

| |

| | |

| SRC_BT_CFG30

| |

| | |

| USDHC2_DATA2

| |

| | |

| USDHC2_DATA2

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 132

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 133

| |

| | LCD

| |

| | LCD-DATA17

| |

| | LCD_DATA17

| |

| | UART7_RX

| |

| | |

| CSI_DATA00

| |

| | |

| EIM_DATA09

| |

| | |

| GPIO3_IO22

| |

| | |

| SRC_BT_CFG25

| |

| | |

| USDHC2_DATA7

| |

| | |

| EPDC_GDSP

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 134

| |

| | LCD

| |

| | LCD-DATA23

| |

| | LCD_DATA23

| |

| | MQS_LEFT

| |

| | |

| ECSPI1_MISO

| |

| | |

| CSI_DATA15

| |

| | |

| EIM_DATA15

| |

| | |

| GPIO3_IO28

| |

| | |

| SRC_BT_CFG31

| |

| | |

| USDHC2_DATA3

| |

| | |

| EPDC_SDCE03

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 135

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 136

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 137

| |

| | LCD

| |

| | LCD-DATA18

| |

| | LCD_DATA18

| |

| | PWM5_OUT

| |

| | |

| CA7_MX6ULL_EVENTO

| |

| | |

| CSI_DATA10

| |

| | |

| EIM_DATA10

| |

| | |

| GPIO3_IO23

| |

| | |

| SRC_BT_CFG26

| |

| | |

| USDHC2_CMD

| |

| | |

| EPDC_BDR01

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 138

| |

| | LCD

| |

| | LCD-DATA19

| |

| | LCD_DATA19

| |

| | PWM6_OUT

| |

| | |

| WDOG1_WDOG_ANY

| |

| | |

| CSI_DATA11

| |

| | |

| EIM_DATA11

| |

| | |

| GPIO3_IO24

| |

| | |

| SRC_BT_CFG27

| |

| | |

| USDHC2_CLK

| |

| | |

| EPDC_VCOM00

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 139

| |

| | LCD

| |

| | LCD-DATA13

| |

| | LCD_DATA13

| |

| | SAI3_TX_BCLK

| |

| | |

| CSI_DATA21

| |

| | |

| EIM_DATA05

| |

| | |

| GPIO3_IO18

| |

| | |

| SRC_BT_CFG13

| |

| | |

| USDHC2_RESET_B

| |

| | |

| EPDC_BDR00

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 140

| |

| | LCD

| |

| | LCD-DATA20

| |

| | LCD_DATA20

| |

| | UART8_TX

| |

| | |

| ECSPI1_SCLK

| |

| | |

| CSI_DATA12

| |

| | |

| EIM_DATA12

| |

| | |

| GPIO3_IO25

| |

| | |

| SRC_BT_CFG28

| |

| | |

| USDHC2_DATA0

| |

| | |

| EPDC_VCOM01

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 141

| |

| | LCD

| |

| | LCD-DATA14

| |

| | LCD_DATA14

| |

| | SAI3_RX_DATA

| |

| | |

| CSI_DATA22

| |

| | |

| EIM_DATA06

| |

| | |

| GPIO3_IO19

| |

| | |

| SRC_BT_CFG14

| |

| | |

| USDHC2_DATA4

| |

| | |

| EPDC_SDSHR

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 142

| |

| | LCD

| |

| | LCD-DATA15

| |

| | LCD_DATA15

| |

| | SAI3_TX_DATA

| |

| | |

| CSI_DATA23

| |

| | |

| EIM_DATA07

| |

| | |

| GPIO3_IO20

| |

| | |

| SRC_BT_CFG15

| |

| | |

| USDHC2_DATA5

| |

| | |

| EPDC_GDRL

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 143

| |

| | LCD

| |

| | LCD-DATA8

| |

| | LCD_DATA08

| |

| | SPDIF_IN

| |

| | |

| CSI_DATA16

| |

| | |

| EIM_DATA00

| |

| | |

| GPIO3_IO13

| |

| | |

| SRC_BT_CFG08

| |

| | |

| FLEXCAN1_TX

| |

| | |

| EPDC_PWRIRQ

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 144

| |

| | LCD

| |

| | LCD-DATA16

| |

| | LCD_DATA16

| |

| | UART7_TX

| |

| | |

| CSI_DATA01

| |

| | |

| EIM_DATA08

| |

| | |

| GPIO3_IO21

| |

| | |

| SRC_BT_CFG24

| |

| | |

| USDHC2_DATA6

| |

| | |

| EPDC_GDCLK

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 145

| |

| | LCD

| |

| | LCD-DATA9

| |

| | LCD_DATA09

| |

| | SAI3_MCLK

| |

| | |

| CSI_DATA17

| |

| | |

| EIM_DATA01

| |

| | |

| GPIO3_IO14

| |

| | |

| SRC_BT_CFG09

| |

| | |

| FLEXCAN1_RX

| |

| | |

| EPDC_PWRWAKE

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 146

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 147

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 148

| |

| | LCD

| |

| | LCD-DATA11

| |

| | LCD_DATA11

| |

| | SAI3_RX_BCLK

| |

| | |

| CSI_DATA19

| |

| | |

| EIM_DATA03

| |

| | |

| GPIO3_IO16

| |

| | |

| SRC_BT_CFG11

| |

| | |

| FLEXCAN2_RX

| |

| | |

| EPDC_PWRSTAT

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 149

| |

| | LCD

| |

| | LCD-DATA5

| |

| | LCD_DATA05

| |

| | UART8_RTS_B

| |

| | |

| ENET2_1588_EVENT2_OUT

| |

| | |

| SPDIF_OUT

| |

| | |

| GPIO3_IO10

| |

| | |

| SRC_BT_CFG05

| |

| | |

| ECSPI1_SS1

| |

| | |

| EPDC_SDDO05

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 150

| |

| | LCD

| |

| | LCD-DATA12

| |

| | LCD_DATA12

| |

| | SAI3_TX_SYNC

| |

| | |

| CSI_DATA20

| |

| | |

| EIM_DATA04

| |

| | |

| GPIO3_IO17

| |

| | |

| SRC_BT_CFG12

| |

| | |

| ECSPI1_RDY

| |

| | |

| EPDC_PWRCTRL00

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 151

| |

| | LCD

| |

| | LCD-DATA6

| |

| | LCD_DATA06

| |

| | UART7_CTS_B

| |

| | |

| ENET2_1588_EVENT3_IN

| |

| | |

| SPDIF_LOCK

| |

| | |

| GPIO3_IO11

| |

| | |

| SRC_BT_CFG06

| |

| | |

| ECSPI1_SS2

| |

| | |

| EPDC_SDDO06

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 152

| |

| | LCD

| |

| | LCD-DATA10

| |

| | LCD_DATA10

| |

| | SAI3_RX_SYNC

| |

| | |

| CSI_DATA18

| |

| | |

| EIM_DATA02

| |

| | |

| GPIO3_IO15

| |

| | |

| SRC_BT_CFG10

| |

| | |

| FLEXCAN2_TX

| |

| | |

| EPDC_PWRCOM

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 153

| |

| | LCD

| |

| | LCD-DATA0

| |

| | LCD_DATA00

| |

| | PWM1_OUT

| |

| | |

| ENET1_1588_EVENT2_IN

| |

| | |

| I2C3_SDA

| |

| | |

| GPIO3_IO05

| |

| | |

| SRC_BT_CFG00

| |

| | |

| SAI1_MCLK

| |

| | |

| EPDC_SDDO00

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 154

| |

| | LCD

| |

| | LCD-DATA3

| |

| | LCD_DATA03

| |

| | PWM4_OUT

| |

| | |

| ENET1_1588_EVENT3_OUT

| |

| | |

| I2C4_SCL

| |

| | |

| GPIO3_IO08

| |

| | |

| SRC_BT_CFG03

| |

| | |

| SAI1_RX_DATA

| |

| | |

| EPDC_SDDO03

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 155

| |

| | LCD

| |

| | LCD-DATA1

| |

| | LCD_DATA01

| |

| | PWM2_OUT

| |

| | |

| ENET1_1588_EVENT2_OUT

| |

| | |

| I2C3_SCL

| |

| | |

| GPIO3_IO06

| |

|

| |

|

| SRC_BT_CFG01

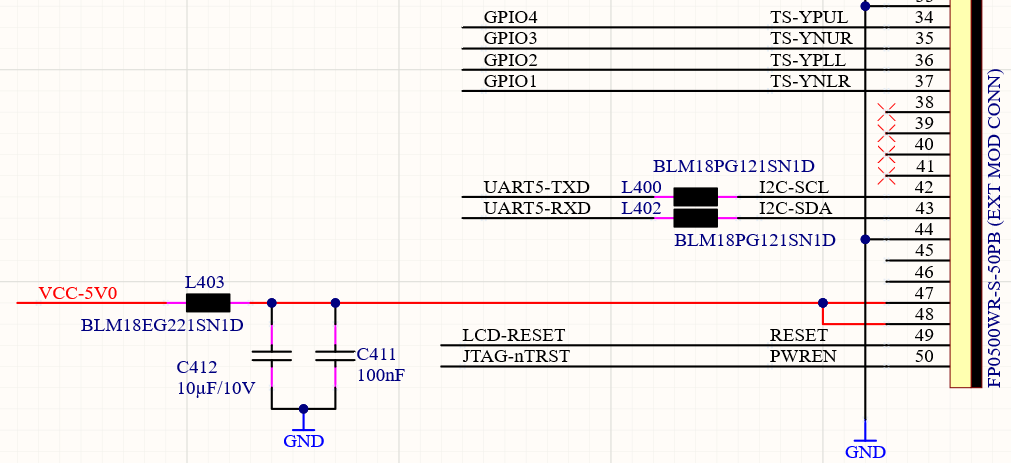

| | == Recommended power supply connection == |

| | | [[File:SL-TFT7-TP-800-480-connection-5V.png|center]]<br> |

| SAI1_TX_SYNC

| |

| | |

| EPDC_SDDO01

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 156

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 157

| |

| | LCD

| |

| | LCD-RESET

| |

| | LCD_RESET

| |

| | LCDIF_CS

| |

| | |

| CA7_MX6ULL_EVENT

| |

| | |

| ISAI3_TX_DATA

| |

| | |

| WDOG1_WDOG_ANY

| |

| | |

| GPIO3_IO04

| |

| | |

| ECSPI2_SS3

| |

| | |

| EPDC_GDOE

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 158

| |

| | LCD

| |

| | LCD-DATA4

| |

| | LCD_DATA04

| |

| | UART8_CTS_B

| |

| | |

| ENET2_1588_EVENT2_IN

| |

| | |

| SPDIF_SR_CLK

| |

| | |

| GPIO3_IO09

| |

| | |

| SRC_BT_CFG04

| |

| | |

| SAI1_TX_DATA

| |

| | |

| EPDC_SDDO04

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 159

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 160

| |

| | LCD

| |

| | LCD-HSYNC

| |

| | LCD_HSYNC

| |

| | LCDIF_RS

| |

| | |

| UART4_CTS_B

| |

| | |

| SAI3_TX_BCLK

| |

| | |

| WDOG3_WDOG_RST_B_DEB

| |

| | |

| GPIO3_IO02

| |

| | |

| ECSPI2_SS1

| |

| | |

| EPDC_SDOE

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 161

| |

| | LCD

| |

| | LCD-CLK

| |

| | LCD_CLK

| |

| | LCDIF_WR_RWN

| |

| | |

| UART4_TX

| |

| | |

| SAI3_MCLK

| |

| | |

| EIM_CS2_B

| |

| | |

| GPIO3_IO00

| |

| | |

| WDOG1_WDOG_RST_B_DEB

| |

| | |

| EPDC_SDCLK

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| 10R resistor connected in series.

| |

| |-

| |

| | 162

| |

| | LCD

| |

| | LCD-VSYNC

| |

| | LCD_VSYNC

| |

| | LCDIF_BUSY

| |

| | |

| UART4_RTS_B

| |

| | |

| SAI3_RX_DATA

| |

| | |

| WDOG2_WDOG_B

| |

| | |

| GPIO3_IO03

| |

| | |

| ECSPI2_SS2

| |

| | |

| EPDC_SDCE00

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 163

| |

| | LCD

| |

| | LCD-ENABLE

| |

| | LCD_ENABLE

| |

| | LCDIF_RD_E

| |

| | |

| UART4_RX

| |

| | |

| SAI3_TX_SYNC

| |

| | |

| EIM_CS3_B

| |

| | |

| GPIO3_IO01

| |

| | |

| ECSPI2_RDY

| |

| | |

| EPDC_SDLE

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 164

| |

| | LCD

| |

| | LCD-DATA2

| |

| | LCD_DATA02

| |

| | PWM3_OUT

| |

| | |

| ENET1_1588_EVENT3_IN

| |

| | |

| I2C4_SDA

| |

| | |

| GPIO3_IO07

| |

| | |

| SRC_BT_CFG02

| |

| | |

| SAI1_TX_BCLK

| |

| | |

| EPDC_SDDO02

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 165

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 166

| |

| | LCD

| |

| | LCD-DATA7

| |

| | LCD_DATA07

| |

| | UART7_RTS_B

| |

| | |

| ENET2_1588_EVENT3_OUT

| |

| | |

| SPDIF_EXT_CLK

| |

| | |

| GPIO3_IO12

| |

| | |

| SRC_BT_CFG07

| |

| | |

| ECSPI1_SS3

| |

| | |

| EPDC_SDDO07

| |

| | |

| | LCD interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 167

| |

| | SDIO

| |

| | SDIO1-D0

| |

| | SD1_DATA0

| |

| | GPT2_COMPARE3

| |

| | |

| SAI2_TX_SYNC

| |

| | |

| FLEXCAN1_TX

| |

| | |

| EIM_ADDR21

| |

| | |

| GPIO2_IO18

| |

| | |

| ANATOP_OTG1_ID

| |

| | |

| | SDIO interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 168

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 169

| |

| | SDIO

| |

| | SDIO1-D3

| |

| | SD1_DATA3

| |

| | GPT2_CAPTURE2

| |

| | |

| SAI2_TX_DATA

| |

| | |

| FLEXCAN2_RX

| |

| | |

| EIM_ADDR24

| |

| | |

| GPIO2_IO21

| |

| | |

| CCM_CLKO2

| |

| | |

| ANATOP_OTG2_ID

| |

| | |

| | SDIO interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 170

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 171

| |

| | SDIO

| |

| | SDIO1-D1

| |

| | SD1_DATA1

| |

| | GPT2_CLK

| |

| | |

| SAI2_TX_BCLK

| |

| | |

| FLEXCAN1_RX

| |

| | |

| EIM_ADDR22

| |

| | |

| GPIO2_IO19

| |

| | |

| USB_OTG2_PWR

| |

| | |

| | SDIO interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 172

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 173

| |

| | SDIO

| |

| | SDIO1-CMD

| |

| | SD1_CMD

| |

| | GPT2_COMPARE1

| |

| | |

| SAI2_RX_SYNC

| |

| | |

| SPDIF_OUT

| |

| | |

| EIM_ADDR19

| |

| | |

| GPIO2_IO16

| |

| | |

| SDMA_EXT_EVENT00

| |

| | |

| USB_OTG1_PWR

| |

| | |

| | SDIO interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 174

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 175

| |

| | SDIO

| |

| | SDIO1-D2

| |

| | SD1_DATA2

| |

| | GPT2_CAPTURE1

| |

| | |

| SAI2_RX_DATA

| |

| | |

| FLEXCAN2_TX

| |

| | |

| EIM_ADDR23

| |

| | |

| GPIO2_IO20

| |

| | |

| CCM_CLKO1

| |

| | |

| USB_OTG2_OC

| |

| | |

| | SDIO interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 176

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 177

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 178

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 179

| |

| | SDIO

| |

| | SDIO1-CLK

| |

| | SD1_CLK

| |

| | GPT2_COMPARE2

| |

| | |

| SAI2_MCLK

| |

| | |

| SPDIF_IN

| |

| | |

| EIM_ADDR20

| |

| | |

| GPIO2_IO17

| |

| | |

| USB_OTG1_OC

| |

| | |

| | SDIO interface signal or universal GPIO with 3.3V logic levels.

| |

| |-

| |

| | 180

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 181

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 182

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 183

| |

| | CSI

| |

| | CSI-PIXCLK

| |

| | CSI_PIXCLK

| |

| | USDHC2_WP

| |

| | |

| RAWNAND_CE3_B

| |

| | |

| I2C1_SCL

| |

| | |

| EIM_OE

| |

| | |

| GPIO4_IO18

| |

| | |

| SNVS_HP_VIO_5

| |

| | |

| UART6_RX

| |

| | |

| ESAI_TX2_RX3

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-WAKE in SOM with WiFi/BT module

| |

| |-

| |

| | 184

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 185

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 186

| |

| | CSI

| |

| | CSI-DATA6

| |

| | CSI_DATA06

| |

| | USDHC2_DATA6

| |

| | |

| ECSPI1_MOSI

| |

| | |

| EIM_AD06

| |

| | |

| GPIO4_IO27

| |

| | |

| SAI1_RX_DATA

| |

| | |

| USDHC1_RESET_BE

| |

| | |

| SAI_TX5_RX0

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-PCM-OUT in SOM with WiFi/BT module

| |

| |-

| |

| | 187

| |

| | CSI

| |

| | CSI-MCLK

| |

| | CSI_MCLK

| |

| | USDHC2_CD_B

| |

| | |

| RAWNAND_CE2_B

| |

| | |

| I2C1_SDA

| |

| | |

| EIM_CS0_B

| |

| | |

| GPIO4_IO17

| |

| | |

| SNVS_HP_VIO_5_CTL

| |

| | |

| UART6_TX

| |

| | |

| ESAI_TX3_RX2

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-ENABLE in SOM with WiFi/BT module

| |

| |-

| |

| | 188

| |

| | CSI

| |

| | CSI-DATA7

| |

| | CSI_DATA07

| |

| | USDHC2_DATA7

| |

| | |

| ECSPI1_MISO

| |

| | |

| EIM_AD07

| |

| | |

| GPIO4_IO28

| |

| | |

| SAI1_TX_DATA

| |

| | |

| USDHC1_VSELECT

| |

| | |

| ESAI_TX0

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-PCM-IN in SOM with WiFi/BT module

| |

| |-

| |

| | 189

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 190

| |

| | CSI

| |

| | CSI-DATA5

| |

| | CSI_DATA05

| |

| | USDHC2_DATA5

| |

| | |

| USDHC2_DATA5

| |

| | |

| EIM_AD05

| |

| | |

| GPIO4_IO26

| |

| | |

| SAI1_TX_BCLK

| |

| | |

| USDHC1_CD_BE

| |

| | |

| SAI_TX_CLK

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-PCM-CLK in SOM with WiFi/BT module

| |

| |-

| |

| | 191

| |

| | CSI

| |

| | CSI-DATA4

| |

| | CSI_DATA04

| |

| | USDHC2_DATA4

| |

| | |

| ECSPI1_SCLK

| |

| | |

| EIM_AD04

| |

| | |

| GPIO4_IO25

| |

| | |

| SAI1_TX_SYNC

| |

| | |

| USDHC1_WP

| |

| | |

| ESAI_TX_FS

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-PCM-SYNC in SOM with WiFi/BT module

| |

| |-

| |

| | 192

| |

| | CSI

| |

| | CSI-DATA3

| |

| | CSI_DATA03

| |

| | USDHC2_DATA3

| |

| | |

| ECSPI2_MISO

| |

| | |

| EIM_AD03

| |

| | |

| GPIO4_IO24

| |

| | |

| SAI1_RX_BCLK

| |

| | |

| UART5_CTS_B

| |

| | |

| ESAI_RX_CLK

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-CTS in SOM with WiFi/BT module

| |

| |-

| |

| | 193

| |

| | CSI

| |

| | CSI-DATA1

| |

| | CSI_DATA01

| |

| | USDHC2_DATA1

| |

| | |

| ECSPI2_SS0

| |

| | |

| EIM_AD01

| |

| | |

| GPIO4_IO22

| |

| | |

| SAI1_MCLK

| |

| | |

| UART5_RX

| |

| | |

| ESAI_RX_HF_CLK

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-TXD in SOM with WiFi/BT module

| |

| |-

| |

| | 194

| |

| | CSI

| |

| | CSI-DATA2

| |

| | CSI_DATA02

| |

| | USDHC2_DATA2

| |

| | |

| ECSPI2_MOSI

| |

| | |

| EIM_AD02

| |

| | |

| GPIO4_IO23

| |

| | |

| SAI1_RX_SYNC

| |

| | |

| UART5_RTS_B

| |

| | |

| ESAI_RX_FS

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-RTS in SOM with WiFi/BT module

| |

| |-

| |

| | 195

| |

| | CSI

| |

| | CSI-DATA0

| |

| | CSI_DATA00

| |

| | USDHC2_DATA0

| |

| | |

| ECSPI2_SCLK

| |

| | |

| EIM_AD00

| |

| | |

| GPIO4_IO21

| |

| | |

| SRC_INT_BOOT

| |

| | |

| UART5_TX

| |

| | |

| ESAI_TX_HF_CLK

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-RXD in SOM with WiFi/BT module

| |

| |-

| |

| | 196

| |

| | Power

| |

| | CSI-VREF

| |

| | -

| |

| | -

| |

| | Leave open if not used.

| |

| |-

| |

| | 197

| |

| | CSI

| |

| | CSI-HSYNC

| |

| | CSI_HSYNC

| |

| | USDHC2_CMD

| |

| | |

| I2C2_SCL

| |

| | |

| EIM_LBA_B

| |

| | |

| GPIO4_IO20

| |

| | |

| PWM8_OUT

| |

| | |

| UART6_CTS_B

| |

| | |

| ESAI_TX1

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| WLAN-HWAKE in SOM with WiFi/BT module

| |

| |-

| |

| | 198

| |

| | CSI

| |

| | CSI-VSYNC

| |

| | CSI_VSYNC

| |

| | SDHC2_CLK

| |

| | |

| I2C2_SDA

| |

| | |

| EIM_RW

| |

| | |

| GPIO4_IO19

| |

| | |

| PWM7_OUT

| |

| | |

| UART6_RTS_B

| |

| | |

| ESAI_TX4_RX1

| |

| | |

| | Video CMOS sensor signal or universal GPIO with 3.3V logic levels.

| |

| BT-HWAKE in SOM with WiFi/BT module

| |

| |-

| |

| | 199

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |-

| |

| | 200

| |

| | Power

| |

| | GND

| |

| | -

| |

| | -

| |

| | -

| |

| |} | |

|

| |

|

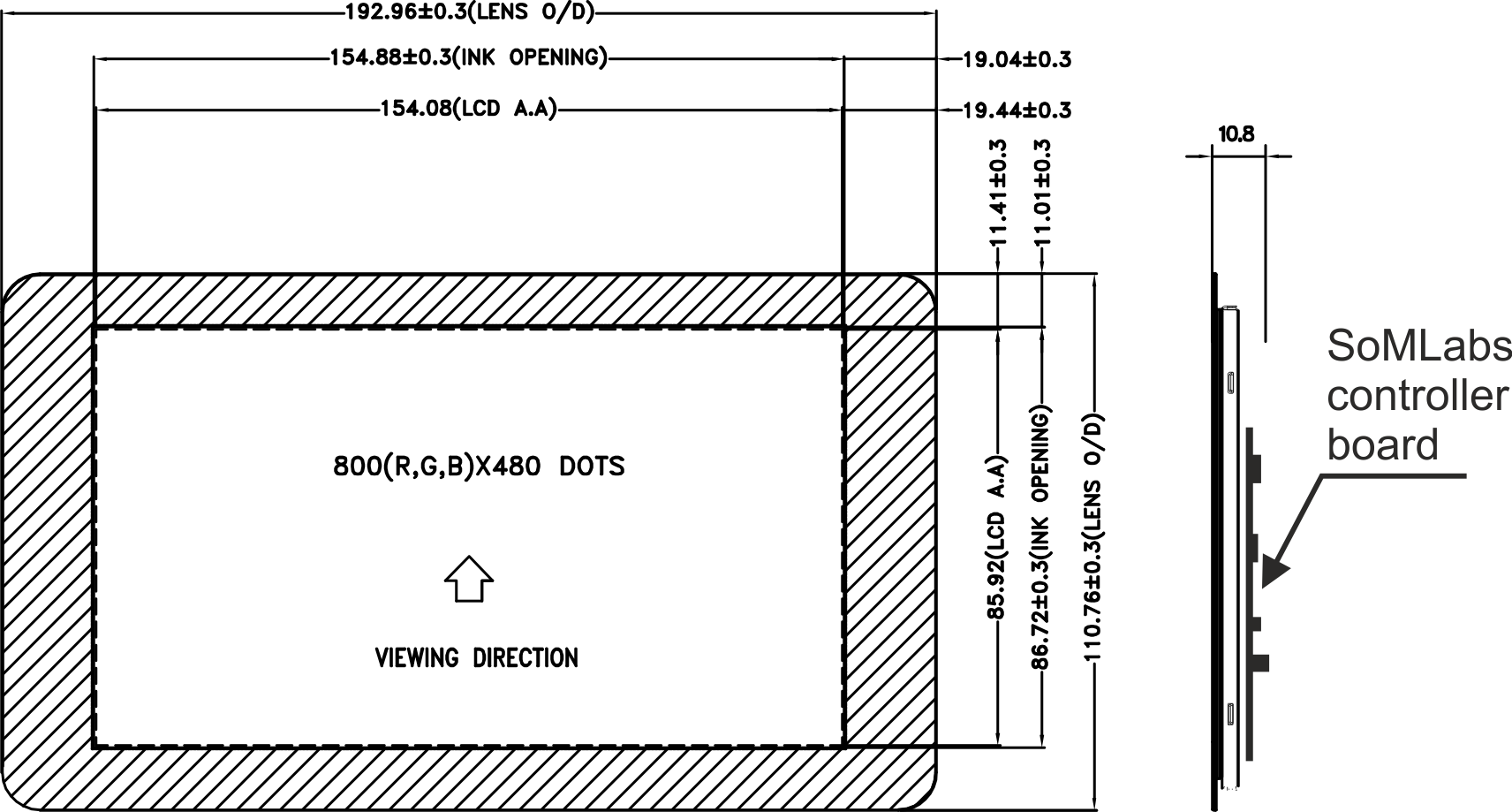

| == Dimensions == | | == Dimensions == |

| [[File:VisionSOM-6ULL Dimiensions.png|center]] | | [[File:SL-TFT7-TP-800-480-wymiary.png|center]] |