VisionSOM-6ULL Datasheet and Pinout: Difference between revisions

From SomLabs Wiki

| (57 intermediate revisions by 3 users not shown) | |||

| Line 5: | Line 5: | ||

The VisionSOM-6ULL family is a SODIMM-sized SoM based on the NXP i.MX6 ULL application processor which features an advanced implementation of a single ARM Cortex-A7 core (at speeds up to 900MHz). | The VisionSOM-6ULL family is a SODIMM-sized SoM based on the NXP i.MX6 ULL application processor which features an advanced implementation of a single ARM Cortex-A7 core (at speeds up to 900MHz). | ||

The VisionSOM-6ULL is a low power highly integrated SoM (System on Module) featuring high computation power and 802.11b/g/n Wi-Fi and Bluetooth | The VisionSOM-6ULL is a low power highly integrated SoM (System on Module) featuring high computation power and 802.11b/g/n Wi-Fi and Bluetooth v5.1 connectivity. The option of integrated, fully certified Wi-Fi and Bluetooth module simplifies the carrier board design and is ideally suited for wireless application. The VisionSOM-6ULL provides a variety memory configuration including flexible range of DDR3L, NAND, eMMC and SD memory card that meets our customers requirements. | ||

The SoM supports connections to a variety of interfaces: two high-speed USB on-the-go with PHY, dual Ethernet, audio, display with touch panel and serial interfaces. In addition, the system supports industrial grade targeting embedded application. | The SoM supports connections to a variety of interfaces: two high-speed USB on-the-go with PHY, dual Ethernet, audio, display with touch panel and serial interfaces. In addition, the system supports industrial grade targeting embedded application. | ||

| Line 20: | Line 20: | ||

* Cash Register | * Cash Register | ||

* 2D barcode scanners and printers | * 2D barcode scanners and printers | ||

* Smart grid | * Smart grid infrastructure | ||

* IoT gateways | * IoT gateways | ||

* Residential | * Residential gateways | ||

* Machine vision equipment | * Machine vision equipment | ||

* Robotics | * Robotics | ||

| Line 32: | Line 32: | ||

* Up to 512MB SDRAM DDR3L | * Up to 512MB SDRAM DDR3L | ||

* Up to 512MB NAND Flash / 32GB eMMC / uSD memory card | * Up to 512MB NAND Flash / 32GB eMMC / uSD memory card | ||

* Optional Murata 802.11b/g/n Wi-Fi and Bluetooth | * Optional Murata 802.11b/g/n Wi-Fi and Bluetooth v5.2 module | ||

* Power-efficient and cost-optimized solution | * Power-efficient and cost-optimized solution | ||

* Ideal for industrial IoT and embedded applications | * Ideal for industrial IoT and embedded applications | ||

| Line 155: | Line 155: | ||

"values" : [ | "values" : [ | ||

{"value" : "0SF", "description" : "No Special Features"}, | {"value" : "0SF", "description" : "No Special Features"}, | ||

{"value" : "1WB", "description" : "Built-in 802.11b/g/n Wi-Fi and Bluetooth | {"value" : "1WB", "description" : "Built-in 802.11b/g/n Wi-Fi and Bluetooth v5.1 Module"} | ||

] | ] | ||

}, | }, | ||

| Line 168: | Line 168: | ||

"values" : [ | "values" : [ | ||

{"value" : "C", "description" : "Consumer: 0 to +70 C "}, | {"value" : "C", "description" : "Consumer: 0 to +70 C "}, | ||

{"value" : " | {"value" : "E", "description" : "Extended with Wi-Fi: -25 to +70 C"}, | ||

{"value" : "I", "description" : "Industrial: -40 to +85 C"} | {"value" : "I", "description" : "Industrial: -40 to +85 C"} | ||

] | ] | ||

| Line 181: | Line 181: | ||

"symbol" : "V", | "symbol" : "V", | ||

"values" : [ | "values" : [ | ||

{"value" : "A", "description" : "Version 1.0"} | {"value" : "A", "description" : "Version 1.0"}, | ||

{"value" : "B", "description" : "Version 1.1"} | |||

] | ] | ||

} | } | ||

| Line 214: | Line 215: | ||

| Industrial range w/o WiFi module | | Industrial range w/o WiFi module | ||

|- | |- | ||

| <center>- | | <center>-25…+70</center> | ||

| Industrial range with WiFi module | | Industrial range with WiFi module | ||

|- | |- | ||

| Line 241: | Line 242: | ||

| V | | V | ||

|- | |- | ||

| +5VIN | |||

| Total Supply Current<sup>1</sup> | |||

| - | | - | ||

| | | 115 | ||

| | | 155 | ||

| | | mA | ||

|- | |- | ||

| VGPIO | | VGPIO | ||

| Line 287: | Line 288: | ||

2. Applying the maximum voltage 3.6V results in shorten lifetime. Recommended value is smaller than 3.5V.<br /> | 2. Applying the maximum voltage 3.6V results in shorten lifetime. Recommended value is smaller than 3.5V.<br /> | ||

== SOM pinout == | == SOM pinout (v1.1 and v1.2) == | ||

Important notes <br /> | |||

1. Detail pin configurations description you can find, edit and arrange in dedicated MEX files (with free "i.MX Pin Tool" configurational tool): | |||

[https://somlabs.com/wp-content/uploads/SoMLabs-VisionSoM-6ULL-NAND-SD-eMMC-noWIFI.zip VisionSOM-6ULL without WiFi module and no SDIO1 on edge connector] or | |||

[https://somlabs.com/wp-content/uploads/SoMLabs-VisionSoM-6ULL-NAND-SD-eMMC-noWIFI-extSDIO1.zip VisionSOM-6ULL without WiFi module and with SDIO1 on edge connector] or | |||

[https://somlabs.com/wp-content/uploads/SoMLabs-VisionSoM-6ULL-NAND-SD-eMMC-WiFi.zip VisionSOM-6ULL witht WiFi module on-board]. <br /> | |||

2. In module version v1.1 the LCD-DATAxx pins are internally used for boot sequence configuration. We recommend to use LCD-DATAxx lines as outputs or using eFuse boot configuration. <br /> | |||

3. In module version v1.2 equipped with NAND Flash the LCD-DATAxx pins are internally used for boot sequence configuration (like in v1.1). We recommend to use LCD-DATAxx lines as outputs or using eFuse boot configuration. <br /> | |||

4. In module version v1.2 equipped with eMMC the boot sequence configuration is stored in eFuse (OTP memory in MPU). All LCD-DATAxx pins can be used freely like all others GPIOs. <br /> | |||

{| class="wikitable" | {| class="wikitable" | ||

! style="text-align: center; font-weight: bold;" | SODIMM PIN | ! style="text-align: center; font-weight: bold;" | SODIMM PIN | ||

! style="text-align: center; font-weight: bold;" | Functional | ! style="text-align: center; font-weight: bold;" | Functional | ||

domain | domain | ||

! style="text-align: center; font-weight: bold;" | Function | ! style="text-align: center; font-weight: bold;" | Function name | ||

name | |||

! style="text-align: center; font-weight: bold;" | i.MX6 UltraLite/ | ! style="text-align: center; font-weight: bold;" | i.MX6 UltraLite/ | ||

ULL Pad Name | ULL Pad Name | ||

| Line 347: | Line 356: | ||

| GPIO5_IO11 | | GPIO5_IO11 | ||

| BOOT-MODE1 BOOT-MODE0 | | BOOT-MODE1 BOOT-MODE0 | ||

00 boot from fuses (default) | 00 boot from fuses (default) | ||

01 serial downloader | 01 serial downloader | ||

10 internal boot | 10 internal boot | ||

11 reserved | 11 reserved | ||

|- | |- | ||

| 8 | | 8 | ||

| Line 357: | Line 371: | ||

| VDD_SNVS_IN | | VDD_SNVS_IN | ||

| - | | - | ||

| Optional external coin battery for SNVS power domain, must be held between 2.9V and 3.3V if the system requires keeping real time and other data on OFF state.Leave open if not used. | | Optional external coin battery for SNVS power domain, must be held between 2.9V and 3.3V if the system requires keeping real time and other data on OFF state. | ||

Leave open if not used. | |||

|- | |- | ||

| 9 | | 9 | ||

| Line 365: | Line 380: | ||

| GPIO5_IO10 | | GPIO5_IO10 | ||

| BOOT-MODE1 BOOT-MODE0 | | BOOT-MODE1 BOOT-MODE0 | ||

00 boot from fuses (default) | 00 boot from fuses (default) | ||

01 serial downloader | 01 serial downloader | ||

10 internal boot | 10 internal boot | ||

11 reserved | 11 reserved | ||

|- | |- | ||

| 10 | | 10 | ||

| Line 418: | Line 438: | ||

| - | | - | ||

| Cold reset negative logic input resets all modules and logic in the IC. | | Cold reset negative logic input resets all modules and logic in the IC. | ||

May be used in addition to internally generated power on reset signal (logical AND, both | May be used in addition to internally generated power on reset signal (logical AND, both internal and external signals are considered active low). | ||

|- | |- | ||

| 17 | | 17 | ||

| Line 565: | Line 585: | ||

| CCM_CLK1_N | | CCM_CLK1_N | ||

| - | | - | ||

| General purpose differential high speed clock input/output.Leave open if not used. | | General purpose differential high speed clock input/output. | ||

Leave open if not used. | |||

|- | |- | ||

| 38 | | 38 | ||

| Line 579: | Line 600: | ||

| CCM_CLK1_P | | CCM_CLK1_P | ||

| - | | - | ||

| General purpose differential high speed clock input/output.Leave open if not used. | | General purpose differential high speed clock input/output. | ||

Leave open if not used. | |||

|- | |- | ||

| 40 | | 40 | ||

| Line 607: | Line 629: | ||

| JTAG_TDI | | JTAG_TDI | ||

| - | | - | ||

| JTAG TDI input line. | | JTAG TDI input line or GPIO. | ||

|- | |- | ||

| 44 | | 44 | ||

| Line 621: | Line 643: | ||

| GPIO1_IO08 | | GPIO1_IO08 | ||

| PWM1_OUT | | PWM1_OUT | ||

WDOG1_WDOG_B | WDOG1_WDOG_B | ||

SPDIF_OUT | SPDIF_OUT | ||

CSI_VSYNC | CSI_VSYNC | ||

USDHC2_VSELECT | USDHC2_VSELECT | ||

CCM_PMIC_RDY | CCM_PMIC_RDY | ||

UART5_RTS_B | UART5_RTS_B | ||

| Universal GPIO with 3.3V logic levels. | | Universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 634: | Line 663: | ||

| JTAG_TMS | | JTAG_TMS | ||

| - | | - | ||

| JTAG TMS input line. | | JTAG TMS input line or GPIO. | ||

|- | |- | ||

| 47 | | 47 | ||

| Line 641: | Line 670: | ||

| GPIO1_IO04 | | GPIO1_IO04 | ||

| ENET1_REF_CLK1 | | ENET1_REF_CLK1 | ||

PWM3_OUT | PWM3_OUT | ||

USB_OTG1_PWR | USB_OTG1_PWR | ||

USDHC1_RESET_B | USDHC1_RESET_B | ||

ENET2_1588_EVENT0_IN | ENET2_1588_EVENT0_IN | ||

UART5_TX | UART5_TX | ||

| Universal GPIO with 3.3V logic levels. | | Universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 653: | Line 688: | ||

| JTAG_TRST_B | | JTAG_TRST_B | ||

| - | | - | ||

| JTAG TRST input line (active L). | | JTAG TRST input line (active L) or GPIO. | ||

|- | |- | ||

| 49 | | 49 | ||

| Line 660: | Line 695: | ||

| GPIO1_IO05 | | GPIO1_IO05 | ||

| ENET2_REF_CLK2 | | ENET2_REF_CLK2 | ||

PWM4_OUT | PWM4_OUT | ||

ANATOP_OTG2_ID | ANATOP_OTG2_ID | ||

CSI_FIELD | CSI_FIELD | ||

USDHC1_VSELECT | USDHC1_VSELECT | ||

ENET2_1588_EVENT0_OUT | ENET2_1588_EVENT0_OUT | ||

UART5_RX | UART5_RX | ||

| Universal GPIO with 3.3V logic levels. | | Universal GPIO with 3.3V logic levels. | ||

WLAN-ENABLE in SOM with WiFi/BT module | WLAN-ENABLE in SOM with WiFi/BT module | ||

| Line 688: | Line 730: | ||

| JTAG_TDO | | JTAG_TDO | ||

| - | | - | ||

| JTAG TDO output line. | | JTAG TDO output line or GPIO. | ||

|- | |- | ||

| 53 | | 53 | ||

| Line 694: | Line 736: | ||

| GPIO-7 | | GPIO-7 | ||

| GPIO1_IO07 | | GPIO1_IO07 | ||

| | | ENET1_MDC | ||

ENET2_MDC | ENET2_MDC | ||

USB_OTG_HOST_MODE | USB_OTG_HOST_MODE | ||

CSI_PIXCLK | CSI_PIXCLK | ||

USDHC2_CD_BCCM_STOP | USDHC2_CD_BCCM_STOP | ||

UART1_RTS_B | UART1_RTS_B | ||

| Universal GPIO with 3.3V logic levels. | | Universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 707: | Line 755: | ||

| JTAG_TCK | | JTAG_TCK | ||

| - | | - | ||

| JTAG TCK input line. | | JTAG TCK input line or GPIO. | ||

Connected to JTAG-TCK line (via separating resistor 10k). | |||

|- | |- | ||

| 55 | | 55 | ||

| Line 714: | Line 763: | ||

| GPIO1_IO03 | | GPIO1_IO03 | ||

| I2C1_SDA | | I2C1_SDA | ||

GPT1_COMPARE3 | GPT1_COMPARE3 | ||

USB_OTG2_OC | USB_OTG2_OC | ||

USDHC1_CD_B | USDHC1_CD_B | ||

CCM_DI0_EXT_CLK | CCM_DI0_EXT_CLK | ||

SRC_TESTER_ACK | SRC_TESTER_ACK | ||

| Universal GPIO with 3.3V logic levels. | | Universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 726: | Line 781: | ||

| GPIO1_IO09 | | GPIO1_IO09 | ||

| PWM2_OUT | | PWM2_OUT | ||

WDOG1_WDOG_ANY | WDOG1_WDOG_ANY | ||

SPDIF_IN | SPDIF_IN | ||

CSI_HSYNC | CSI_HSYNC | ||

USDHC2_RESET_B | USDHC2_RESET_B | ||

USDHC1_RESET_B | USDHC1_RESET_B | ||

UART5_CTS_B | UART5_CTS_B | ||

| Universal GPIO with 3.3V logic levels. | | Universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 739: | Line 801: | ||

| UART1_TX_DATA | | UART1_TX_DATA | ||

| ENET1_RDATA02 | | ENET1_RDATA02 | ||

I2C3_SCL | I2C3_SCL | ||

CSI_DATA02 | CSI_DATA02 | ||

GPT1_COMPARE1 | GPT1_COMPARE1 | ||

GPIO1_IO16 | GPIO1_IO16 | ||

SPDIF_OUT | SPDIF_OUT | ||

UART5_TX | UART5_TX | ||

| Default: UART1 TxD | |||

| Default: UART1 TxD output or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 58 | | 58 | ||

| Line 752: | Line 821: | ||

| GPIO1_IO02 | | GPIO1_IO02 | ||

| I2C1_SCL | | I2C1_SCL | ||

GPT1_COMPARE2 | GPT1_COMPARE2 | ||

USB_OTG2_PWR | USB_OTG2_PWR | ||

ENET1_REF_CLK_25M | ENET1_REF_CLK_25M | ||

USDHC1_WPS | USDHC1_WPS | ||

DMA_EXT_EVENT00 | DMA_EXT_EVENT00 | ||

SRC_ANY_PU_RESET | SRC_ANY_PU_RESET | ||

UART1_TX | UART1_TX | ||

| Universal GPIO with 3.3V logic levels. | | Universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 780: | Line 857: | ||

| GPIO1_IO06 | | GPIO1_IO06 | ||

| ENET1_MDIO | | ENET1_MDIO | ||

ENET2_MDIO | ENET2_MDIO | ||

USB_OTG_PWR_WAKE | USB_OTG_PWR_WAKE | ||

CSI_MCLK | CSI_MCLK | ||

USDHC2_WPCCM_WAIT | USDHC2_WPCCM_WAIT | ||

CCM_REF_EN_B | CCM_REF_EN_B | ||

UART1_CTS_B | UART1_CTS_B | ||

| Universal GPIO with 3.3V logic levels. | | Universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 793: | Line 877: | ||

| GPIO1_IO01 | | GPIO1_IO01 | ||

| I2C2_SDA | | I2C2_SDA | ||

GPT1_COMPARE1 | GPT1_COMPARE1 | ||

USB_OTG1_OC | USB_OTG1_OC | ||

ENET2_REF_CLK2 | ENET2_REF_CLK2 | ||

MQS_LEFT | MQS_LEFT | ||

ENET1_1588_EVENT0_OUT | ENET1_1588_EVENT0_OUT | ||

SRC_EARLY_RESET | SRC_EARLY_RESET | ||

WDOG1_WDOG_B | WDOG1_WDOG_B | ||

| Universal GPIO with 3.3V logic levels. | | Universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 807: | Line 899: | ||

| UART1_RX_DATA | | UART1_RX_DATA | ||

| ENET1_RDATA03 | | ENET1_RDATA03 | ||

I2C3_SDA | I2C3_SDA | ||

CSI_DATA03 | CSI_DATA03 | ||

GPT1_CLK | GPT1_CLK | ||

GPIO1_IO17 | GPIO1_IO17 | ||

SPDIF_IN | SPDIF_IN | ||

UART5_RX | UART5_RX | ||

| Default: UART1 RxD | |||

| Default: UART1 RxD input or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 64 | | 64 | ||

| Line 820: | Line 919: | ||

| GPIO1_IO00 | | GPIO1_IO00 | ||

| I2C2_SCL | | I2C2_SCL | ||

GPT1_CAPTURE1 | GPT1_CAPTURE1 | ||

ANATOP_OTG1_ID | ANATOP_OTG1_ID | ||

ENET1_REF_CLK1 | ENET1_REF_CLK1 | ||

MQS_RIGHT | MQS_RIGHT | ||

ENET1_1588_EVENT0_IN | ENET1_1588_EVENT0_IN | ||

SRC_SYSTEM_RESET | SRC_SYSTEM_RESET | ||

WDOG3_WDOG_B | WDOG3_WDOG_B | ||

| Universal GPIO with 3.3V logic levels. | | Universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 834: | Line 941: | ||

| UART2_TX_DATA | | UART2_TX_DATA | ||

| ENET1_TDATA02 | | ENET1_TDATA02 | ||

I2C4_SCL | I2C4_SCL | ||

CSI_DATA06 | CSI_DATA06 | ||

GPT1_CAPTURE1 | GPT1_CAPTURE1 | ||

GPIO1_IO20 | GPIO1_IO20 | ||

ECSPI3_SS0 | ECSPI3_SS0 | ||

| Default: UART2 TxD | |||

| Default: UART2 TxD output or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 66 | | 66 | ||

| Line 846: | Line 959: | ||

| UART1_CTS_B | | UART1_CTS_B | ||

| ENET1_RX_CLK | | ENET1_RX_CLK | ||

USDHC1_WP | USDHC1_WP | ||

CSI_DATA04 | CSI_DATA04 | ||

ENET2_1588_EVENT1_IN | ENET2_1588_EVENT1_IN | ||

GPIO1_IO18 | GPIO1_IO18 | ||

USDHC2_WP | USDHC2_WP | ||

UART5_CTS_B | UART5_CTS_B | ||

| Default: UART1 CTS | |||

| Default: UART1 CTS output or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 67 | | 67 | ||

| Line 859: | Line 979: | ||

| UART2_RX_DATA | | UART2_RX_DATA | ||

| ENET1_TDATA03 | | ENET1_TDATA03 | ||

I2C4_SDA | I2C4_SDA | ||

CSI_DATA07 | CSI_DATA07 | ||

GPT1_CAPTURE2 | GPT1_CAPTURE2 | ||

GPIO1_IO21 | GPIO1_IO21 | ||

SJC_DONE | SJC_DONE | ||

ECSPI3_SCLK | ECSPI3_SCLK | ||

| Default: UART2 RxD | |||

| Default: UART2 RxD input or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 68 | | 68 | ||

| Line 872: | Line 999: | ||

| UART5_RX_DATA | | UART5_RX_DATA | ||

| ENET2_COL | | ENET2_COL | ||

I2C2_SDA | I2C2_SDA | ||

CSI_DATA15 | CSI_DATA15 | ||

CSU_CSU_INT_DEB | CSU_CSU_INT_DEB | ||

GPIO1_IO31 | GPIO1_IO31 | ||

ECSPI2_MISO | ECSPI2_MISO | ||

EPDC_PWRCTRL03 | EPDC_PWRCTRL03 | ||

| Default: UART5 RxD | |||

| Default: UART5 RxD input or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 69 | | 69 | ||

| Line 885: | Line 1,019: | ||

| UART3_TX_DATA | | UART3_TX_DATA | ||

| ENET2_RDATA02 | | ENET2_RDATA02 | ||

CSI_DATA01 | CSI_DATA01 | ||

UART2_CTS_B | UART2_CTS_B | ||

GPIO1_IO24 | GPIO1_IO24 | ||

SJC_JTAG_ACT | SJC_JTAG_ACT | ||

| Default: UART3 TxD | |||

| Default: UART3 TxD input or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 70 | | 70 | ||

| Line 910: | Line 1,049: | ||

| UART2_CTS_B | | UART2_CTS_B | ||

| ENET1_CRS | | ENET1_CRS | ||

FLEXCAN2_TXCSI_DATA08 | FLEXCAN2_TXCSI_DATA08 | ||

GPT1_COMPARE2 | GPT1_COMPARE2 | ||

GPIO1_IO22 | GPIO1_IO22 | ||

SJC_DE_B | SJC_DE_B | ||

ECSPI3_MOSI | ECSPI3_MOSI | ||

| Default: UART2 CTS | |||

| Default: UART2 CTS output or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 73 | | 73 | ||

| Line 922: | Line 1,067: | ||

| UART3_RX_DATA | | UART3_RX_DATA | ||

| ENET2_RDATA03 | | ENET2_RDATA03 | ||

CSI_DATA00 | CSI_DATA00 | ||

UART2_RTS_B | UART2_RTS_B | ||

GPIO1_IO25 | GPIO1_IO25 | ||

EPIT1_OUT | EPIT1_OUT | ||

| Default: UART3 RxD | |||

| Default: UART3 RxD input or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 74 | | 74 | ||

| Line 933: | Line 1,083: | ||

| UART1_RTS_B | | UART1_RTS_B | ||

| ENET1_TX_ER | | ENET1_TX_ER | ||

USDHC1_CD_BCSI_DATA05 | USDHC1_CD_BCSI_DATA05 | ||

ENET2_1588_EVENT1_OUT | ENET2_1588_EVENT1_OUT | ||

GPIO1_IO19 | GPIO1_IO19 | ||

USDHC2_CD_B | USDHC2_CD_B | ||

UART5_RTS_B | UART5_RTS_B | ||

| Default: UART1 RTS | |||

| Default: UART1 RTS input or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 75 | | 75 | ||

| Line 945: | Line 1,101: | ||

| UART4_TX_DATA | | UART4_TX_DATA | ||

| ENET2_TDATA02 | | ENET2_TDATA02 | ||

I2C1_SCL | I2C1_SCL | ||

CSI_DATA12 | CSI_DATA12 | ||

CSU_CSU_ALARM_AUT02 | CSU_CSU_ALARM_AUT02 | ||

GPIO1_IO28 | GPIO1_IO28 | ||

ECSPI2_SCLK | ECSPI2_SCLK | ||

| Default: UART4 TxD | |||

| Default: UART4 TxD output or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 76 | | 76 | ||

| Line 957: | Line 1,119: | ||

| UART3_CTS_B | | UART3_CTS_B | ||

| ENET2_RX_CLK | | ENET2_RX_CLK | ||

FLEXCAN1_TX | FLEXCAN1_TX | ||

CSI_DATA10 | CSI_DATA10 | ||

ENET1_1588_EVENT1_IN | ENET1_1588_EVENT1_IN | ||

GPIO1_IO26 | GPIO1_IO26 | ||

EPIT2_OUT | EPIT2_OUT | ||

| Default: UART3 CTS | |||

| Default: UART3 CTS output or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 77 | | 77 | ||

| Line 969: | Line 1,137: | ||

| UART4_RX_DATA | | UART4_RX_DATA | ||

| ENET2_TDATA03 | | ENET2_TDATA03 | ||

I2C1_SDA | I2C1_SDA | ||

CSI_DATA13 | CSI_DATA13 | ||

CSU_CSU_ALARM_AUT01 | CSU_CSU_ALARM_AUT01 | ||

GPIO1_IO29 | GPIO1_IO29 | ||

ECSPI2_SS0 | ECSPI2_SS0 | ||

EPDC_PWRCTRL01 | EPDC_PWRCTRL01 | ||

| Default: UART4 RxD | |||

| Default: UART4 RxD input or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 78 | | 78 | ||

| Line 982: | Line 1,157: | ||

| UART2_RTS_B | | UART2_RTS_B | ||

| ENET1_COL | | ENET1_COL | ||

FLEXCAN2_RX | FLEXCAN2_RX | ||

CSI_DATA09 | CSI_DATA09 | ||

GPT1_COMPARE3 | GPT1_COMPARE3 | ||

GPIO1_IO23 | GPIO1_IO23 | ||

SJC_FAIL | SJC_FAIL | ||

ECSPI3_MISO | ECSPI3_MISO | ||

| Default: UART2 RTS | |||

| Default: UART2 RTS input or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 79 | | 79 | ||

| Line 995: | Line 1,177: | ||

| UART5_TX_DATA | | UART5_TX_DATA | ||

| GPIO1_IO30 | | GPIO1_IO30 | ||

ECSPI2_MOSI | ECSPI2_MOSI | ||

EPDC_PWRCTRL02 | EPDC_PWRCTRL02 | ||

ENET2_CRS | ENET2_CRS | ||

I2C2_SCL | I2C2_SCL | ||

CSI_DATA14 | CSI_DATA14 | ||

CSU_CSU_ALARM_AUT00 | CSU_CSU_ALARM_AUT00 | ||

| Default: UART5 TxD | |||

| Default: UART5 TxD output or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 80 | | 80 | ||

| Line 1,008: | Line 1,197: | ||

| UART3_RTS_B | | UART3_RTS_B | ||

| ENET2_TX_ER | | ENET2_TX_ER | ||

FLEXCAN1_RX | FLEXCAN1_RX | ||

CSI_DATA11 | CSI_DATA11 | ||

ENET1_1588_EVENT1_OUT | ENET1_1588_EVENT1_OUT | ||

GPIO1_IO27 | GPIO1_IO27 | ||

WDOG1_WDOG_B | WDOG1_WDOG_B | ||

| Default: UART3 RTS | |||

| Default: UART3 RTS input or universal GPIO with 3.3V logic levels. | |||

|- | |- | ||

| 81 | | 81 | ||

| Line 1,132: | Line 1,327: | ||

| ENET1_RX_DATA0 | | ENET1_RX_DATA0 | ||

| UART4_RTS_B | | UART4_RTS_B | ||

PWM1_OUT | PWM1_OUT | ||

CSI_DATA16 | CSI_DATA16 | ||

FLEXCAN1_TX | FLEXCAN1_TX | ||

GPIO2_IO00 | GPIO2_IO00 | ||

KPP_ROW00 | KPP_ROW00 | ||

USDHC1_LCTL | USDHC1_LCTL | ||

EPDC_SDCE04 | EPDC_SDCE04 | ||

| Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,153: | Line 1,356: | ||

| ENET1_RX_DATA1 | | ENET1_RX_DATA1 | ||

| UART4_CTS_B | | UART4_CTS_B | ||

PWM2_OUT | PWM2_OUT | ||

CSI_DATA17 | CSI_DATA17 | ||

FLEXCAN1_RX | FLEXCAN1_RX | ||

GPIO2_IO01 | GPIO2_IO01 | ||

KPP_COL00 | KPP_COL00 | ||

USDHC2_LCTL | USDHC2_LCTL | ||

EPDC_SDCE05 | EPDC_SDCE05 | ||

| Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,174: | Line 1,385: | ||

| ENET1_RX_EN | | ENET1_RX_EN | ||

| UART5_RTS_B | | UART5_RTS_B | ||

CSI_DATA18 | CSI_DATA18 | ||

FLEXCAN2_TX | FLEXCAN2_TX | ||

GPIO2_IO02 | GPIO2_IO02 | ||

KPP_ROW01 | KPP_ROW01 | ||

USDHC1_VSELECT | USDHC1_VSELECT | ||

EPDC_SDCE06 | EPDC_SDCE06 | ||

| Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,208: | Line 1,426: | ||

| ENET2_TX_CLK | | ENET2_TX_CLK | ||

| UART8_CTS_B | | UART8_CTS_B | ||

ECSPI4_MISO | ECSPI4_MISO | ||

ENET2_REF_CLK2 | ENET2_REF_CLK2 | ||

GPIO2_IO14 | GPIO2_IO14 | ||

KPP_ROW07 | KPP_ROW07 | ||

ANATOP_OTG2_ID | ANATOP_OTG2_ID | ||

EPDC_SDDO14 | EPDC_SDDO14 | ||

| Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

10R resistor connected in series. | |||

|- | |- | ||

| 106 | | 106 | ||

| Line 1,242: | Line 1,468: | ||

| ENET2_RX_ER | | ENET2_RX_ER | ||

| UART8_RTS_B | | UART8_RTS_B | ||

ECSPI4_SS0 | ECSPI4_SS0 | ||

EIM_ADDR25 | EIM_ADDR25 | ||

GPIO2_IO15 | GPIO2_IO15 | ||

KPP_COL07 | KPP_COL07 | ||

WDOG1_WDOG_ANY | WDOG1_WDOG_ANY | ||

EPDC_SDDO15 | EPDC_SDDO15 | ||

| Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

Connected to WDOG-B line. | |||

|- | |- | ||

| 110 | | 110 | ||

| Line 1,262: | Line 1,496: | ||

| ENET2_RX_DATA0 | | ENET2_RX_DATA0 | ||

| UART6_TX | | UART6_TX | ||

I2C3_SCL | I2C3_SCL | ||

ENET1_MDIO | ENET1_MDIO | ||

GPIO2_IO08 | GPIO2_IO08 | ||

KPP_ROW04 | KPP_ROW04 | ||

USB_OTG1_PWR | USB_OTG1_PWR | ||

EPDC_SDDO08 | EPDC_SDDO08 | ||

| Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,282: | Line 1,523: | ||

| ENET2_RX_DATA1 | | ENET2_RX_DATA1 | ||

| UART6_RX | | UART6_RX | ||

I2C3_SDA | I2C3_SDA | ||

ENET1_MDC | ENET1_MDC | ||

GPIO2_IO09 | GPIO2_IO09 | ||

KPP_COL04 | KPP_COL04 | ||

USB_OTG1_OCE | USB_OTG1_OCE | ||

PDC_SDDO09 | PDC_SDDO09 | ||

| Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,295: | Line 1,543: | ||

| ENET1_TX_EN | | ENET1_TX_EN | ||

| UART6_RTS_B | | UART6_RTS_B | ||

PWM6_OUT | PWM6_OUT | ||

CSI_DATA21 | CSI_DATA21 | ||

ENET2_MDC | ENET2_MDC | ||

GPIO2_IO05 | GPIO2_IO05 | ||

KPP_COL02 | KPP_COL02 | ||

WDOG2_WDOG_RST_B_DEB | WDOG2_WDOG_RST_B_DEB | ||

EPDC_SDCE09 | EPDC_SDCE09 | ||

| Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,323: | Line 1,579: | ||

| ENET2_RX_EN | | ENET2_RX_EN | ||

| UART7_TX | | UART7_TX | ||

I2C4_SCL | I2C4_SCL | ||

EIM_ADDR26 | EIM_ADDR26 | ||

GPIO2_IO10 | GPIO2_IO10 | ||

KPP_ROW05 | KPP_ROW05 | ||

ENET1_REF_CLK_25M | ENET1_REF_CLK_25M | ||

EPDC_SDDO10 | EPDC_SDDO10 | ||

| Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,336: | Line 1,599: | ||

| ENET1_TX_CLK | | ENET1_TX_CLK | ||

| UART7_CTS_B | | UART7_CTS_B | ||

PWM7_OUT | PWM7_OUT | ||

CSI_DATA22 | CSI_DATA22 | ||

ENET1_REF_CLK1 | ENET1_REF_CLK1 | ||

GPIO2_IO06 | GPIO2_IO06 | ||

KPP_ROW03 | KPP_ROW03 | ||

GPT1_CLK | GPT1_CLK | ||

EPDC_SDOED | EPDC_SDOED | ||

| Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

10R resistor connected in series. | |||

|- | |- | ||

| 119 | | 119 | ||

| Line 1,350: | Line 1,622: | ||

| ENET2_TX_DATA1 | | ENET2_TX_DATA1 | ||

| UART8_TX | | UART8_TX | ||

ECSPI4_SCLK | ECSPI4_SCLK | ||

EIM_EB_B03 | EIM_EB_B03 | ||

GPIO2_IO12 | GPIO2_IO12 | ||

KPP_ROW06 | KPP_ROW06 | ||

USB_OTG2_PWR | USB_OTG2_PWR | ||

EPDC_SDDO12 | EPDC_SDDO12 | ||

| Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,370: | Line 1,649: | ||

| ENET2_TX_EN | | ENET2_TX_EN | ||

| UART8_RX | | UART8_RX | ||

ECSPI4_MOSI | ECSPI4_MOSI | ||

EIM_ACLK_FREERUN | EIM_ACLK_FREERUN | ||

GPIO2_IO13 | GPIO2_IO13 | ||

KPP_COL06 | KPP_COL06 | ||

USB_OTG2_OC | USB_OTG2_OC | ||

EPDC_SDDO13 | EPDC_SDDO13 | ||

| | | | ||

|- | |- | ||

| Line 1,383: | Line 1,669: | ||

| ENET1_TX_DATA0 | | ENET1_TX_DATA0 | ||

| UART5_CTS_B | | UART5_CTS_B | ||

CSI_DATA19 | CSI_DATA19 | ||

FLEXCAN2_RX | FLEXCAN2_RX | ||

GPIO2_IO03 | GPIO2_IO03 | ||

KPP_COL01 | KPP_COL01 | ||

USDHC2_VSELECT | USDHC2_VSELECT | ||

EPDC_SDCE07 | EPDC_SDCE07 | ||

| Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,396: | Line 1,689: | ||

| ENET2_TX_DATA0 | | ENET2_TX_DATA0 | ||

| UART7_RX | | UART7_RX | ||

I2C4_SDA | I2C4_SDA | ||

EIM_EB_B02 | EIM_EB_B02 | ||

GPIO2_IO11 | GPIO2_IO11 | ||

KPP_COL05 | KPP_COL05 | ||

EPDC_SDDO11 | EPDC_SDDO11 | ||

| Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,408: | Line 1,707: | ||

| ENET1_TX_DATA1 | | ENET1_TX_DATA1 | ||

| UART6_CTS_B | | UART6_CTS_B | ||

PWM5_OUT | PWM5_OUT | ||

CSI_DATA20 | CSI_DATA20 | ||

ENET2_MDIO | ENET2_MDIO | ||

GPIO2_IO04 | GPIO2_IO04 | ||

KPP_ROW02 | KPP_ROW02 | ||

WDOG1_WDOG_RST_B_DEB | WDOG1_WDOG_RST_B_DEB | ||

EPDC_SDCE08 | EPDC_SDCE08 | ||

| Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,429: | Line 1,736: | ||

| ENET1_RX_ER | | ENET1_RX_ER | ||

| UART7_RTS_B | | UART7_RTS_B | ||

PWM8_OUT | PWM8_OUT | ||

CSI_DATA23 | CSI_DATA23 | ||

EIM_CRE | EIM_CRE | ||

GPIO2_IO07 | GPIO2_IO07 | ||

KPP_COL03 | KPP_COL03 | ||

GPT1_CAPTURE2 | GPT1_CAPTURE2 | ||

EPDC_SDOEZ | EPDC_SDOEZ | ||

| Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | | Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,457: | Line 1,772: | ||

| LCD_DATA21 | | LCD_DATA21 | ||

| UART8_RX | | UART8_RX | ||

ECSPI1_SS0 | ECSPI1_SS0 | ||

CSI_DATA13 | CSI_DATA13 | ||

EIM_DATA13 | EIM_DATA13 | ||

GPIO3_IO26 | GPIO3_IO26 | ||

SRC_BT_CFG29 | SRC_BT_CFG29 | ||

USDHC2_DATA1 | USDHC2_DATA1 | ||

EPDC_SDCE01 | EPDC_SDCE01 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 130 | | 130 | ||

| Line 1,478: | Line 1,802: | ||

| LCD_DATA22 | | LCD_DATA22 | ||

| MQS_RIGHT | | MQS_RIGHT | ||

ECSPI1_MOSI | ECSPI1_MOSI | ||

CSI_DATA14 | CSI_DATA14 | ||

EIM_DATA14 | EIM_DATA14 | ||

GPIO3_IO27 | GPIO3_IO27 | ||

SRC_BT_CFG30 | SRC_BT_CFG30 | ||

USDHC2_DATA2 | USDHC2_DATA2 | ||

USDHC2_DATA2 | USDHC2_DATA2 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 132 | | 132 | ||

| Line 1,499: | Line 1,832: | ||

| LCD_DATA17 | | LCD_DATA17 | ||

| UART7_RX | | UART7_RX | ||

CSI_DATA00 | CSI_DATA00 | ||

EIM_DATA09 | EIM_DATA09 | ||

GPIO3_IO22 | GPIO3_IO22 | ||

SRC_BT_CFG25 | SRC_BT_CFG25 | ||

USDHC2_DATA7 | USDHC2_DATA7 | ||

EPDC_GDSP | EPDC_GDSP | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 134 | | 134 | ||

| Line 1,512: | Line 1,853: | ||

| LCD_DATA23 | | LCD_DATA23 | ||

| MQS_LEFT | | MQS_LEFT | ||

ECSPI1_MISO | ECSPI1_MISO | ||

CSI_DATA15 | CSI_DATA15 | ||

EIM_DATA15 | EIM_DATA15 | ||

GPIO3_IO28 | GPIO3_IO28 | ||

SRC_BT_CFG31 | SRC_BT_CFG31 | ||

USDHC2_DATA3 | USDHC2_DATA3 | ||

EPDC_SDCE03 | EPDC_SDCE03 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 135 | | 135 | ||

| Line 1,540: | Line 1,890: | ||

| LCD_DATA18 | | LCD_DATA18 | ||

| PWM5_OUT | | PWM5_OUT | ||

CA7_MX6ULL_EVENTO | CA7_MX6ULL_EVENTO | ||

CSI_DATA10 | CSI_DATA10 | ||

EIM_DATA10 | EIM_DATA10 | ||

GPIO3_IO23 | GPIO3_IO23 | ||

SRC_BT_CFG26 | SRC_BT_CFG26 | ||

USDHC2_CMD | USDHC2_CMD | ||

EPDC_BDR01 | EPDC_BDR01 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 138 | | 138 | ||

| Line 1,554: | Line 1,913: | ||

| LCD_DATA19 | | LCD_DATA19 | ||

| PWM6_OUT | | PWM6_OUT | ||

WDOG1_WDOG_ANY | WDOG1_WDOG_ANY | ||

CSI_DATA11 | CSI_DATA11 | ||

EIM_DATA11 | EIM_DATA11 | ||

GPIO3_IO24 | GPIO3_IO24 | ||

SRC_BT_CFG27 | SRC_BT_CFG27 | ||

USDHC2_CLK | USDHC2_CLK | ||

EPDC_VCOM00 | EPDC_VCOM00 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 139 | | 139 | ||

| Line 1,568: | Line 1,936: | ||

| LCD_DATA13 | | LCD_DATA13 | ||

| SAI3_TX_BCLK | | SAI3_TX_BCLK | ||

CSI_DATA21 | CSI_DATA21 | ||

EIM_DATA05 | EIM_DATA05 | ||

GPIO3_IO18 | GPIO3_IO18 | ||

SRC_BT_CFG13 | SRC_BT_CFG13 | ||

USDHC2_RESET_B | USDHC2_RESET_B | ||

EPDC_BDR00 | EPDC_BDR00 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 140 | | 140 | ||

| Line 1,581: | Line 1,957: | ||

| LCD_DATA20 | | LCD_DATA20 | ||

| UART8_TX | | UART8_TX | ||

ECSPI1_SCLK | ECSPI1_SCLK | ||

CSI_DATA12 | CSI_DATA12 | ||

EIM_DATA12 | EIM_DATA12 | ||

GPIO3_IO25 | GPIO3_IO25 | ||

SRC_BT_CFG28 | SRC_BT_CFG28 | ||

USDHC2_DATA0 | USDHC2_DATA0 | ||

EPDC_VCOM01 | EPDC_VCOM01 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 141 | | 141 | ||

| Line 1,595: | Line 1,980: | ||

| LCD_DATA14 | | LCD_DATA14 | ||

| SAI3_RX_DATA | | SAI3_RX_DATA | ||

CSI_DATA22 | CSI_DATA22 | ||

EIM_DATA06 | EIM_DATA06 | ||

GPIO3_IO19 | GPIO3_IO19 | ||

SRC_BT_CFG14 | SRC_BT_CFG14 | ||

USDHC2_DATA4 | USDHC2_DATA4 | ||

EPDC_SDSHR | EPDC_SDSHR | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 142 | | 142 | ||

| Line 1,608: | Line 2,001: | ||

| LCD_DATA15 | | LCD_DATA15 | ||

| SAI3_TX_DATA | | SAI3_TX_DATA | ||

CSI_DATA23 | CSI_DATA23 | ||

EIM_DATA07 | EIM_DATA07 | ||

GPIO3_IO20 | GPIO3_IO20 | ||

SRC_BT_CFG15 | SRC_BT_CFG15 | ||

USDHC2_DATA5 | USDHC2_DATA5 | ||

EPDC_GDRL | EPDC_GDRL | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 143 | | 143 | ||

| Line 1,621: | Line 2,022: | ||

| LCD_DATA08 | | LCD_DATA08 | ||

| SPDIF_IN | | SPDIF_IN | ||

CSI_DATA16 | CSI_DATA16 | ||

EIM_DATA00 | EIM_DATA00 | ||

GPIO3_IO13 | GPIO3_IO13 | ||

SRC_BT_CFG08 | SRC_BT_CFG08 | ||

FLEXCAN1_TX | FLEXCAN1_TX | ||

EPDC_PWRIRQ | EPDC_PWRIRQ | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 144 | | 144 | ||

| Line 1,634: | Line 2,043: | ||

| LCD_DATA16 | | LCD_DATA16 | ||

| UART7_TX | | UART7_TX | ||

CSI_DATA01 | CSI_DATA01 | ||

EIM_DATA08 | EIM_DATA08 | ||

GPIO3_IO21 | GPIO3_IO21 | ||

SRC_BT_CFG24 | SRC_BT_CFG24 | ||

USDHC2_DATA6 | USDHC2_DATA6 | ||

EPDC_GDCLK | EPDC_GDCLK | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 145 | | 145 | ||

| Line 1,647: | Line 2,064: | ||

| LCD_DATA09 | | LCD_DATA09 | ||

| SAI3_MCLK | | SAI3_MCLK | ||

CSI_DATA17 | CSI_DATA17 | ||

EIM_DATA01 | EIM_DATA01 | ||

GPIO3_IO14 | GPIO3_IO14 | ||

SRC_BT_CFG09 | SRC_BT_CFG09 | ||

FLEXCAN1_RX | FLEXCAN1_RX | ||

EPDC_PWRWAKE | EPDC_PWRWAKE | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 146 | | 146 | ||

| Line 1,674: | Line 2,099: | ||

| LCD_DATA11 | | LCD_DATA11 | ||

| SAI3_RX_BCLK | | SAI3_RX_BCLK | ||

CSI_DATA19 | CSI_DATA19 | ||

EIM_DATA03 | EIM_DATA03 | ||

GPIO3_IO16 | GPIO3_IO16 | ||

SRC_BT_CFG11 | SRC_BT_CFG11 | ||

FLEXCAN2_RX | FLEXCAN2_RX | ||

EPDC_PWRSTAT | EPDC_PWRSTAT | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 149 | | 149 | ||

| Line 1,687: | Line 2,120: | ||

| LCD_DATA05 | | LCD_DATA05 | ||

| UART8_RTS_B | | UART8_RTS_B | ||

ENET2_1588_EVENT2_OUT | ENET2_1588_EVENT2_OUT | ||

SPDIF_OUT | SPDIF_OUT | ||

GPIO3_IO10 | GPIO3_IO10 | ||

SRC_BT_CFG05 | SRC_BT_CFG05 | ||

ECSPI1_SS1 | ECSPI1_SS1 | ||

EPDC_SDDO05 | EPDC_SDDO05 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 150 | | 150 | ||

| Line 1,700: | Line 2,141: | ||

| LCD_DATA12 | | LCD_DATA12 | ||

| SAI3_TX_SYNC | | SAI3_TX_SYNC | ||

CSI_DATA20 | CSI_DATA20 | ||

EIM_DATA04 | EIM_DATA04 | ||

GPIO3_IO17 | GPIO3_IO17 | ||

SRC_BT_CFG12 | SRC_BT_CFG12 | ||

ECSPI1_RDY | ECSPI1_RDY | ||

EPDC_PWRCTRL00 | EPDC_PWRCTRL00 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 151 | | 151 | ||

| Line 1,713: | Line 2,162: | ||

| LCD_DATA06 | | LCD_DATA06 | ||

| UART7_CTS_B | | UART7_CTS_B | ||

ENET2_1588_EVENT3_IN | ENET2_1588_EVENT3_IN | ||

SPDIF_LOCK | SPDIF_LOCK | ||

GPIO3_IO11 | GPIO3_IO11 | ||

SRC_BT_CFG06 | SRC_BT_CFG06 | ||

ECSPI1_SS2 | ECSPI1_SS2 | ||

EPDC_SDDO06 | EPDC_SDDO06 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 152 | | 152 | ||

| Line 1,726: | Line 2,183: | ||

| LCD_DATA10 | | LCD_DATA10 | ||

| SAI3_RX_SYNC | | SAI3_RX_SYNC | ||

CSI_DATA18 | CSI_DATA18 | ||

EIM_DATA02 | EIM_DATA02 | ||

GPIO3_IO15 | GPIO3_IO15 | ||

SRC_BT_CFG10 | SRC_BT_CFG10 | ||

FLEXCAN2_TX | FLEXCAN2_TX | ||

EPDC_PWRCOM | EPDC_PWRCOM | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 153 | | 153 | ||

| Line 1,739: | Line 2,204: | ||

| LCD_DATA00 | | LCD_DATA00 | ||

| PWM1_OUT | | PWM1_OUT | ||

ENET1_1588_EVENT2_IN | ENET1_1588_EVENT2_IN | ||

I2C3_SDA | I2C3_SDA | ||

GPIO3_IO05 | GPIO3_IO05 | ||

SRC_BT_CFG00 | SRC_BT_CFG00 | ||

SAI1_MCLK | SAI1_MCLK | ||

EPDC_SDDO00 | EPDC_SDDO00 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 154 | | 154 | ||

| Line 1,752: | Line 2,225: | ||

| LCD_DATA03 | | LCD_DATA03 | ||

| PWM4_OUT | | PWM4_OUT | ||

ENET1_1588_EVENT3_OUT | ENET1_1588_EVENT3_OUT | ||

I2C4_SCL | I2C4_SCL | ||

GPIO3_IO08 | GPIO3_IO08 | ||

SRC_BT_CFG03 | SRC_BT_CFG03 | ||

SAI1_RX_DATA | SAI1_RX_DATA | ||

EPDC_SDDO03 | EPDC_SDDO03 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 155 | | 155 | ||

| Line 1,765: | Line 2,246: | ||

| LCD_DATA01 | | LCD_DATA01 | ||

| PWM2_OUT | | PWM2_OUT | ||

ENET1_1588_EVENT2_OUT | ENET1_1588_EVENT2_OUT | ||

I2C3_SCL | I2C3_SCL | ||

GPIO3_IO06 | GPIO3_IO06 | ||

SRC_BT_CFG01 | SRC_BT_CFG01 | ||

SAI1_TX_SYNC | SAI1_TX_SYNC | ||

EPDC_SDDO01 | EPDC_SDDO01 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 156 | | 156 | ||

| Line 1,785: | Line 2,274: | ||

| LCD_RESET | | LCD_RESET | ||

| LCDIF_CS | | LCDIF_CS | ||

CA7_MX6ULL_EVENT | CA7_MX6ULL_EVENT | ||

ISAI3_TX_DATA | ISAI3_TX_DATA | ||

WDOG1_WDOG_ANY | WDOG1_WDOG_ANY | ||

GPIO3_IO04 | GPIO3_IO04 | ||

ECSPI2_SS3 | ECSPI2_SS3 | ||

EPDC_GDOE | EPDC_GDOE | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,798: | Line 2,294: | ||

| LCD_DATA04 | | LCD_DATA04 | ||

| UART8_CTS_B | | UART8_CTS_B | ||

ENET2_1588_EVENT2_IN | ENET2_1588_EVENT2_IN | ||

SPDIF_SR_CLK | SPDIF_SR_CLK | ||

GPIO3_IO09 | GPIO3_IO09 | ||

SRC_BT_CFG04 | SRC_BT_CFG04 | ||

SAI1_TX_DATA | SAI1_TX_DATA | ||

EPDC_SDDO04 | EPDC_SDDO04 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 159 | | 159 | ||

| Line 1,818: | Line 2,322: | ||

| LCD_HSYNC | | LCD_HSYNC | ||

| LCDIF_RS | | LCDIF_RS | ||

UART4_CTS_B | UART4_CTS_B | ||

SAI3_TX_BCLK | SAI3_TX_BCLK | ||

WDOG3_WDOG_RST_B_DEB | WDOG3_WDOG_RST_B_DEB | ||

GPIO3_IO02 | GPIO3_IO02 | ||

ECSPI2_SS1 | ECSPI2_SS1 | ||

EPDC_SDOE | EPDC_SDOE | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,831: | Line 2,342: | ||

| LCD_CLK | | LCD_CLK | ||

| LCDIF_WR_RWN | | LCDIF_WR_RWN | ||

UART4_TX | UART4_TX | ||

SAI3_MCLK | SAI3_MCLK | ||

EIM_CS2_B | EIM_CS2_B | ||

GPIO3_IO00 | GPIO3_IO00 | ||

WDOG1_WDOG_RST_B_DEB | WDOG1_WDOG_RST_B_DEB | ||

EPDC_SDCLK | EPDC_SDCLK | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

10R resistor connected in series. | |||

|- | |- | ||

| 162 | | 162 | ||

| Line 1,844: | Line 2,363: | ||

| LCD_VSYNC | | LCD_VSYNC | ||

| LCDIF_BUSY | | LCDIF_BUSY | ||

UART4_RTS_B | UART4_RTS_B | ||

SAI3_RX_DATA | SAI3_RX_DATA | ||

WDOG2_WDOG_B | WDOG2_WDOG_B | ||

GPIO3_IO03 | GPIO3_IO03 | ||

ECSPI2_SS2 | ECSPI2_SS2 | ||

EPDC_SDCE00 | EPDC_SDCE00 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,857: | Line 2,383: | ||

| LCD_ENABLE | | LCD_ENABLE | ||

| LCDIF_RD_E | | LCDIF_RD_E | ||

UART4_RX | UART4_RX | ||

SAI3_TX_SYNC | SAI3_TX_SYNC | ||

EIM_CS3_B | EIM_CS3_B | ||

GPIO3_IO01 | GPIO3_IO01 | ||

ECSPI2_RDY | ECSPI2_RDY | ||

EPDC_SDLE | EPDC_SDLE | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

|- | |- | ||

| Line 1,870: | Line 2,403: | ||

| LCD_DATA02 | | LCD_DATA02 | ||

| PWM3_OUT | | PWM3_OUT | ||

ENET1_1588_EVENT3_IN | ENET1_1588_EVENT3_IN | ||

I2C4_SDA | I2C4_SDA | ||

GPIO3_IO07 | GPIO3_IO07 | ||

SRC_BT_CFG02 | SRC_BT_CFG02 | ||

SAI1_TX_BCLK | SAI1_TX_BCLK | ||

EPDC_SDDO02 | EPDC_SDDO02 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 165 | | 165 | ||

| Line 1,890: | Line 2,431: | ||

| LCD_DATA07 | | LCD_DATA07 | ||

| UART7_RTS_B | | UART7_RTS_B | ||

ENET2_1588_EVENT3_OUT | ENET2_1588_EVENT3_OUT | ||

SPDIF_EXT_CLK | SPDIF_EXT_CLK | ||

GPIO3_IO12 | GPIO3_IO12 | ||

SRC_BT_CFG07 | SRC_BT_CFG07 | ||

ECSPI1_SS3 | ECSPI1_SS3 | ||

EPDC_SDDO07 | EPDC_SDDO07 | ||

| LCD interface signal or universal GPIO with 3.3V logic levels. | | LCD interface signal or universal GPIO with 3.3V logic levels. | ||

Internally used as boot configuration input (Notes 2, 3 & 4). | |||

|- | |- | ||

| 167 | | 167 | ||

| Line 1,903: | Line 2,452: | ||

| SD1_DATA0 | | SD1_DATA0 | ||

| GPT2_COMPARE3 | | GPT2_COMPARE3 | ||

SAI2_TX_SYNC | SAI2_TX_SYNC | ||

FLEXCAN1_TX | FLEXCAN1_TX | ||

EIM_ADDR21 | EIM_ADDR21 | ||

GPIO2_IO18 | GPIO2_IO18 | ||

ANATOP_OTG1_ID | ANATOP_OTG1_ID | ||

| SDIO interface signal or universal GPIO with 3.3V logic levels. | | SDIO interface signal or universal GPIO with 3.3V logic levels. | ||

Used by WiFi/BT module if built-in SOM. | |||

Built-in internal pull-up 10k. | |||

|- | |- | ||

| 168 | | 168 | ||

| Line 1,922: | Line 2,482: | ||

| SD1_DATA3 | | SD1_DATA3 | ||

| GPT2_CAPTURE2 | | GPT2_CAPTURE2 | ||

SAI2_TX_DATA | SAI2_TX_DATA | ||

FLEXCAN2_RX | FLEXCAN2_RX | ||

EIM_ADDR24 | EIM_ADDR24 | ||

GPIO2_IO21 | GPIO2_IO21 | ||

CCM_CLKO2 | CCM_CLKO2 | ||

ANATOP_OTG2_ID | ANATOP_OTG2_ID | ||

| SDIO interface signal or universal GPIO with 3.3V logic levels. | | SDIO interface signal or universal GPIO with 3.3V logic levels. | ||

Used by WiFi/BT module if built-in SOM. | |||

Built-in internal pull-up 10k. | |||

|- | |- | ||

| 170 | | 170 | ||

| Line 1,942: | Line 2,515: | ||

| SD1_DATA1 | | SD1_DATA1 | ||

| GPT2_CLK | | GPT2_CLK | ||

SAI2_TX_BCLK | SAI2_TX_BCLK | ||

FLEXCAN1_RX | FLEXCAN1_RX | ||

EIM_ADDR22 | EIM_ADDR22 | ||

GPIO2_IO19 | GPIO2_IO19 | ||

USB_OTG2_PWR | USB_OTG2_PWR | ||

| SDIO interface signal or universal GPIO with 3.3V logic levels. | | SDIO interface signal or universal GPIO with 3.3V logic levels. | ||

Used by WiFi/BT module if built-in SOM. | |||

Built-in internal pull-up 10k. | |||

|- | |- | ||

| 172 | | 172 | ||

| Line 1,961: | Line 2,546: | ||

| SD1_CMD | | SD1_CMD | ||

| GPT2_COMPARE1 | | GPT2_COMPARE1 | ||

SAI2_RX_SYNC | SAI2_RX_SYNC | ||

SPDIF_OUT | SPDIF_OUT | ||

EIM_ADDR19 | EIM_ADDR19 | ||

GPIO2_IO16 | GPIO2_IO16 | ||

SDMA_EXT_EVENT00 | SDMA_EXT_EVENT00 | ||

USB_OTG1_PWR | USB_OTG1_PWR | ||

| SDIO interface signal or universal GPIO with 3.3V logic levels. | | SDIO interface signal or universal GPIO with 3.3V logic levels. | ||

Used by WiFi/BT module if built-in SOM. | |||

Built-in internal pull-up 10k. | |||

|- | |- | ||

| 174 | | 174 | ||

| Line 1,981: | Line 2,579: | ||

| SD1_DATA2 | | SD1_DATA2 | ||

| GPT2_CAPTURE1 | | GPT2_CAPTURE1 | ||

SAI2_RX_DATA | SAI2_RX_DATA | ||

FLEXCAN2_TX | FLEXCAN2_TX | ||

EIM_ADDR23 | EIM_ADDR23 | ||

GPIO2_IO20 | GPIO2_IO20 | ||

CCM_CLKO1 | CCM_CLKO1 | ||

USB_OTG2_OC | USB_OTG2_OC | ||

| SDIO interface signal or universal GPIO with 3.3V logic levels. | | SDIO interface signal or universal GPIO with 3.3V logic levels. | ||

Used by WiFi/BT module if built-in SOM. | |||

Built-in internal pull-up 10k. | |||

|- | |- | ||

| 176 | | 176 | ||

| Line 2,015: | Line 2,626: | ||

| SD1_CLK | | SD1_CLK | ||

| GPT2_COMPARE2 | | GPT2_COMPARE2 | ||

SAI2_MCLK | SAI2_MCLK | ||

SPDIF_IN | SPDIF_IN | ||

EIM_ADDR20 | EIM_ADDR20 | ||

GPIO2_IO17 | GPIO2_IO17 | ||

USB_OTG1_OC | USB_OTG1_OC | ||

| SDIO interface signal or universal GPIO with 3.3V logic levels. | | SDIO interface signal or universal GPIO with 3.3V logic levels. | ||

Used by WiFi/BT module if built-in SOM. | |||

|- | |- | ||

| 180 | | 180 | ||

| Line 2,048: | Line 2,666: | ||

| CSI_PIXCLK | | CSI_PIXCLK | ||

| USDHC2_WP | | USDHC2_WP | ||

RAWNAND_CE3_B | RAWNAND_CE3_B | ||

I2C1_SCL | I2C1_SCL | ||

EIM_OE | EIM_OE | ||

GPIO4_IO18 | GPIO4_IO18 | ||

SNVS_HP_VIO_5 | SNVS_HP_VIO_5 | ||

UART6_RX | UART6_RX | ||

ESAI_TX2_RX3 | ESAI_TX2_RX3 | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-WAKE in SOM with WiFi/BT module | BT-WAKE in SOM with WiFi/BT module | ||

| Line 2,077: | Line 2,703: | ||

| CSI_DATA06 | | CSI_DATA06 | ||

| USDHC2_DATA6 | | USDHC2_DATA6 | ||

ECSPI1_MOSI | ECSPI1_MOSI | ||

EIM_AD06 | EIM_AD06 | ||

GPIO4_IO27 | GPIO4_IO27 | ||

SAI1_RX_DATA | SAI1_RX_DATA | ||

USDHC1_RESET_BE | USDHC1_RESET_BE | ||

SAI_TX5_RX0 | SAI_TX5_RX0 | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-PCM-OUT in SOM with WiFi/BT module | BT-PCM-OUT in SOM with WiFi/BT module | ||

| Line 2,091: | Line 2,724: | ||

| CSI_MCLK | | CSI_MCLK | ||

| USDHC2_CD_B | | USDHC2_CD_B | ||

RAWNAND_CE2_B | RAWNAND_CE2_B | ||

I2C1_SDA | I2C1_SDA | ||

EIM_CS0_B | EIM_CS0_B | ||

GPIO4_IO17 | GPIO4_IO17 | ||

SNVS_HP_VIO_5_CTL | SNVS_HP_VIO_5_CTL | ||

UART6_TX | UART6_TX | ||

ESAI_TX3_RX2 | ESAI_TX3_RX2 | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-ENABLE in SOM with WiFi/BT module | BT-ENABLE in SOM with WiFi/BT module | ||

| Line 2,106: | Line 2,747: | ||

| CSI_DATA07 | | CSI_DATA07 | ||

| USDHC2_DATA7 | | USDHC2_DATA7 | ||

ECSPI1_MISO | ECSPI1_MISO | ||

EIM_AD07 | EIM_AD07 | ||

GPIO4_IO28 | GPIO4_IO28 | ||

SAI1_TX_DATA | SAI1_TX_DATA | ||

USDHC1_VSELECT | USDHC1_VSELECT | ||

ESAI_TX0 | ESAI_TX0 | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-PCM-IN in SOM with WiFi/BT module | BT-PCM-IN in SOM with WiFi/BT module | ||

| Line 2,127: | Line 2,775: | ||

| CSI_DATA05 | | CSI_DATA05 | ||

| USDHC2_DATA5 | | USDHC2_DATA5 | ||

USDHC2_DATA5 | USDHC2_DATA5 | ||

EIM_AD05 | EIM_AD05 | ||

GPIO4_IO26 | GPIO4_IO26 | ||

SAI1_TX_BCLK | SAI1_TX_BCLK | ||

USDHC1_CD_BE | USDHC1_CD_BE | ||

SAI_TX_CLK | SAI_TX_CLK | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-PCM-CLK in SOM with WiFi/BT module | BT-PCM-CLK in SOM with WiFi/BT module | ||

| Line 2,141: | Line 2,796: | ||

| CSI_DATA04 | | CSI_DATA04 | ||

| USDHC2_DATA4 | | USDHC2_DATA4 | ||

ECSPI1_SCLK | ECSPI1_SCLK | ||

EIM_AD04 | EIM_AD04 | ||

GPIO4_IO25 | GPIO4_IO25 | ||

SAI1_TX_SYNC | SAI1_TX_SYNC | ||

USDHC1_WP | USDHC1_WP | ||

ESAI_TX_FS | ESAI_TX_FS | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-PCM-SYNC in SOM with WiFi/BT module | BT-PCM-SYNC in SOM with WiFi/BT module | ||

| Line 2,155: | Line 2,817: | ||

| CSI_DATA03 | | CSI_DATA03 | ||

| USDHC2_DATA3 | | USDHC2_DATA3 | ||

ECSPI2_MISO | ECSPI2_MISO | ||

EIM_AD03 | EIM_AD03 | ||

GPIO4_IO24 | GPIO4_IO24 | ||

SAI1_RX_BCLK | SAI1_RX_BCLK | ||

UART5_CTS_B | UART5_CTS_B | ||

ESAI_RX_CLK | ESAI_RX_CLK | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-CTS in SOM with WiFi/BT module | BT-CTS in SOM with WiFi/BT module | ||

| Line 2,169: | Line 2,838: | ||

| CSI_DATA01 | | CSI_DATA01 | ||

| USDHC2_DATA1 | | USDHC2_DATA1 | ||

ECSPI2_SS0 | ECSPI2_SS0 | ||

EIM_AD01 | EIM_AD01 | ||

GPIO4_IO22 | GPIO4_IO22 | ||

SAI1_MCLK | SAI1_MCLK | ||

UART5_RX | UART5_RX | ||

ESAI_RX_HF_CLK | ESAI_RX_HF_CLK | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-TXD in SOM with WiFi/BT module | BT-TXD in SOM with WiFi/BT module | ||

| Line 2,183: | Line 2,859: | ||

| CSI_DATA02 | | CSI_DATA02 | ||

| USDHC2_DATA2 | | USDHC2_DATA2 | ||

ECSPI2_MOSI | ECSPI2_MOSI | ||

EIM_AD02 | EIM_AD02 | ||

GPIO4_IO23 | GPIO4_IO23 | ||

SAI1_RX_SYNC | SAI1_RX_SYNC | ||

UART5_RTS_B | UART5_RTS_B | ||

ESAI_RX_FS | ESAI_RX_FS | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-RTS in SOM with WiFi/BT module | BT-RTS in SOM with WiFi/BT module | ||

| Line 2,197: | Line 2,880: | ||

| CSI_DATA00 | | CSI_DATA00 | ||

| USDHC2_DATA0 | | USDHC2_DATA0 | ||

ECSPI2_SCLK | ECSPI2_SCLK | ||

EIM_AD00 | EIM_AD00 | ||

GPIO4_IO21 | GPIO4_IO21 | ||

SRC_INT_BOOT | SRC_INT_BOOT | ||

UART5_TX | UART5_TX | ||

ESAI_TX_HF_CLK | ESAI_TX_HF_CLK | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-RXD in SOM with WiFi/BT module | BT-RXD in SOM with WiFi/BT module | ||

| Line 2,218: | Line 2,908: | ||

| CSI_HSYNC | | CSI_HSYNC | ||

| USDHC2_CMD | | USDHC2_CMD | ||

I2C2_SCL | I2C2_SCL | ||

EIM_LBA_B | EIM_LBA_B | ||

GPIO4_IO20 | GPIO4_IO20 | ||

PWM8_OUT | PWM8_OUT | ||

UART6_CTS_B | UART6_CTS_B | ||

ESAI_TX1 | ESAI_TX1 | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

WLAN-HWAKE in SOM with WiFi/BT module | WLAN-HWAKE in SOM with WiFi/BT module | ||

| Line 2,232: | Line 2,929: | ||

| CSI_VSYNC | | CSI_VSYNC | ||

| SDHC2_CLK | | SDHC2_CLK | ||

I2C2_SDA | I2C2_SDA | ||

EIM_RW | EIM_RW | ||

GPIO4_IO19 | GPIO4_IO19 | ||

PWM7_OUT | PWM7_OUT | ||

UART6_RTS_B | UART6_RTS_B | ||

ESAI_TX4_RX1 | ESAI_TX4_RX1 | ||

| Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | | Video CMOS sensor signal or universal GPIO with 3.3V logic levels. | ||

BT-HWAKE in SOM with WiFi/BT module | BT-HWAKE in SOM with WiFi/BT module | ||

Latest revision as of 12:55, 31 October 2023

VisionSOM-6ULL Datasheet and Pinout

General description

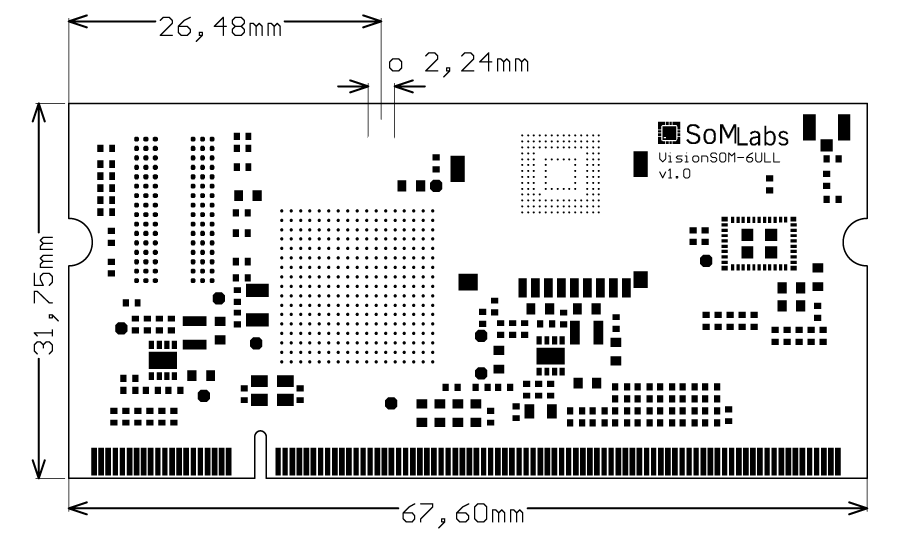

The VisionSOM-6ULL family is a SODIMM-sized SoM based on the NXP i.MX6 ULL application processor which features an advanced implementation of a single ARM Cortex-A7 core (at speeds up to 900MHz).

The VisionSOM-6ULL is a low power highly integrated SoM (System on Module) featuring high computation power and 802.11b/g/n Wi-Fi and Bluetooth v5.1 connectivity. The option of integrated, fully certified Wi-Fi and Bluetooth module simplifies the carrier board design and is ideally suited for wireless application. The VisionSOM-6ULL provides a variety memory configuration including flexible range of DDR3L, NAND, eMMC and SD memory card that meets our customers requirements.

The SoM supports connections to a variety of interfaces: two high-speed USB on-the-go with PHY, dual Ethernet, audio, display with touch panel and serial interfaces. In addition, the system supports industrial grade targeting embedded application.

SOMLabs also provides a complete hardware and software development board for the SoM in the form of a carrier board and optional TFT display and touch panel.

Applications

- Industrial embedded Linux computer

- Home Appliances

- Home Automation – Smart Home

- Human-machine Interfaces (HMI)

- Point-of-sales (POS) terminals

- Cash Register

- 2D barcode scanners and printers

- Smart grid infrastructure

- IoT gateways

- Residential gateways

- Machine vision equipment

- Robotics

- Fitness/outdoor equipment

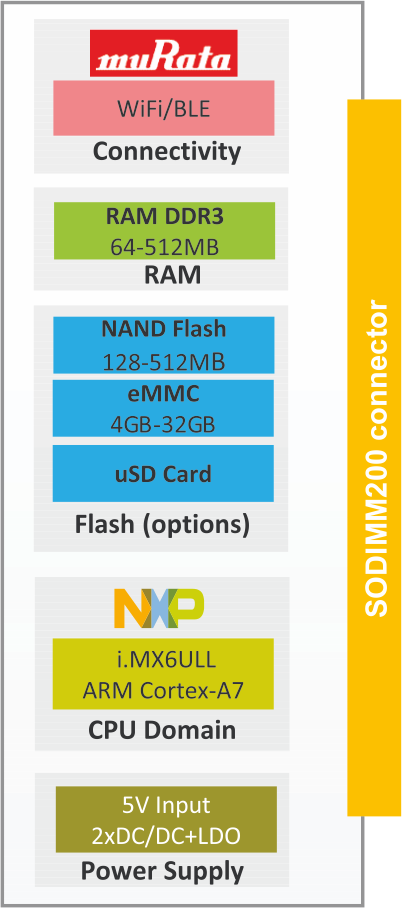

Features

- Powered by NXP i.MX 6ULL application processor

- Core clock up to 900MHz

- Up to 512MB SDRAM DDR3L

- Up to 512MB NAND Flash / 32GB eMMC / uSD memory card

- Optional Murata 802.11b/g/n Wi-Fi and Bluetooth v5.2 module

- Power-efficient and cost-optimized solution

- Ideal for industrial IoT and embedded applications

- Integrated security features

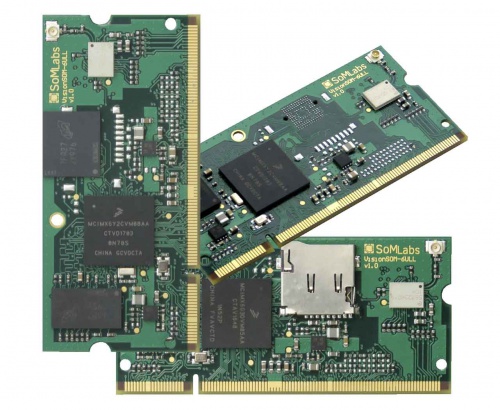

Pictures of SOM versions

| Version | Photo |

|---|---|

| eMMC |

|

| micro-SD |

|

| NAND Flash |

|

| Wi-Fi is available for all memory variants configurations. |

Ordering info

| SLS | Product type SLS - System on Module |

| N | SOM Name 1 - VisionSOM SODIMM200 |

| 6 | CPU Family 6 - i.MX6 |

| CpuType | CPU Type Y0 - i.MX6 ULL Y0 Y1 - i.MX6 ULL Y1 Y2 - i.MX6 ULL Y2 |

| Clock | CPU Clock Speed 528C - 528MHz 792C - 792MHz 900C - 900MHz |

| RamSize | DDR3 RAM Size 64R - 64MB 128R - 128MB 256R - 256MB 512R - 512MB |

| FlashSize | Flash Size Type and Density SD - MicroSD connector 128N - 128MB NAND 256N - 256MB NAND 512N - 512MB NAND 04GE - 4GB eMMC 08GE - 8GB eMMC 16GE - 16GB eMMC 32GE - 32GB eMMC |

| SF | Special Features 0SF - No Special Features 1WB - Built-in 802.11b/g/n Wi-Fi and Bluetooth v5.1 Module |

| TEMP | Operating Temperature C - Consumer: 0 to +70 C E - Extended with Wi-Fi: -25 to +70 C I - Industrial: -40 to +85 C |

| V | SOM Version A - Version 1.0 B - Version 1.1 |

Block Diagram

Operating ranges

| Parameter | Value | Unit | Comment |

|---|---|---|---|

| Power Supply | Connected to +5VIN SODIMM pin | ||

| Input GPIO voltage | - | ||

| Environment temperature1 | oC | Industrial range w/o WiFi module | |

| Industrial range with WiFi module | |||

| Consumer range |

Note:

1. Maximum MPU junction temperature is +105oC (industrial version) or +95oC (consumer version).

Electrical parameters

| SOM signal name |

Parameter | Value | Units | ||

|---|---|---|---|---|---|

| Min. | Typ. | Max. | |||

| +5VIN | Supply Voltage | 4.0 | 5.0 | 5.5 | V |

| +5VIN | Total Supply Current1 | - | 115 | 155 | mA |

| VGPIO | GPIO Input Voltage | 0 | 3.3 | 3.62 | V |

| +3.3VOUT | SOM Internal LDO Output Current |

- | - | 0.5 | A |

| USB-OTGx-VBUS | USB Supply | 4.40 | - | 5.5 | V |

| VDD-COIN-3V | SNVS Backup Battery Supply |

2.66 | - | 3.6 | V |

| - | ADC Inputs Voltage | 0 | - | 3.3 | V |

Notes:

1. Excluding external load connected to +3.3VOUT lines.

2. Applying the maximum voltage 3.6V results in shorten lifetime. Recommended value is smaller than 3.5V.

SOM pinout (v1.1 and v1.2)

Important notes

1. Detail pin configurations description you can find, edit and arrange in dedicated MEX files (with free "i.MX Pin Tool" configurational tool):

VisionSOM-6ULL without WiFi module and no SDIO1 on edge connector or

VisionSOM-6ULL without WiFi module and with SDIO1 on edge connector or

VisionSOM-6ULL witht WiFi module on-board.

2. In module version v1.1 the LCD-DATAxx pins are internally used for boot sequence configuration. We recommend to use LCD-DATAxx lines as outputs or using eFuse boot configuration.

3. In module version v1.2 equipped with NAND Flash the LCD-DATAxx pins are internally used for boot sequence configuration (like in v1.1). We recommend to use LCD-DATAxx lines as outputs or using eFuse boot configuration.

4. In module version v1.2 equipped with eMMC the boot sequence configuration is stored in eFuse (OTP memory in MPU). All LCD-DATAxx pins can be used freely like all others GPIOs.

| SODIMM PIN | Functional

domain |

Function name | i.MX6 UltraLite/

ULL Pad Name |

Alternate functions | Description (refer to i.MX6 UltraLite/ULL manuals for details) |

|---|---|---|---|---|---|

| 1 | Power | GND | - | - | - |

| 2 | Power | GND | - | - | - |

| 3 | Ctrl | PMIC-STBY-REQ | CCM_PMIC_STBY_REQ | - | Output, leave open if not used. |

| 4 | Ctrl | MX6-POR-B | - | - | External warm reset input, active L. |

| 5 | Ctrl | PMIC-ON-REQ | SNVS_PMIC_ON_REQ | - | Output, leave open if not used. |

| 6 | Power | VDD-SNVS-3V3 | VDD_SNVS_IN | - | SNVS backup power supply must be held between 2.9V and 3.3V if the system requires keeping real time and other data on OFF state. Internally connected to +3.3V, leave open. |

| 7 | BOOT | BOOT-MODE1 | BOOT_MODE1 | GPIO5_IO11 | BOOT-MODE1 BOOT-MODE0

00 boot from fuses (default) 01 serial downloader 10 internal boot 11 reserved |

| 8 | Power | VDD-COIN-3V | VDD_SNVS_IN | - | Optional external coin battery for SNVS power domain, must be held between 2.9V and 3.3V if the system requires keeping real time and other data on OFF state.

Leave open if not used. |

| 9 | BOOT | BOOT-MODE0 | BOOT_MODE0 | GPIO5_IO10 | BOOT-MODE1 BOOT-MODE0

00 boot from fuses (default) 01 serial downloader 10 internal boot 11 reserved |

| 10 | GPIO-SNVS | SNVS-TAMPER9 | SNVS_TAMPER9 | GPIO5_IO09 | Tamper input (SNVS power domain) or GPIO 3.3V. |

| 11 | USB | USB-OTG2-VBUS | USB_OTG2_VBUS | - | +5V USB bus. Leave open if not used. |

| 12 | GPIO-SNVS | SNVS-TAMPER5 | SNVS_TAMPER5 | GPIO5_IO05 | Tamper input (SNVS power domain) or GPIO 3.3V. |

| 13 | USB | USB-OTG1-VBUS | USB_OTG1_VBUS | - | +5V USB bus. Leave open if not used. |

| 14 | Ctrl | ONOFF | SRC_RESET_B | Input for power interrupt generation. Leave open if not used. | |

| 15 | Power | GND | - | - | - |

| 16 | Ctrl | POR-B | POR_B | - | Cold reset negative logic input resets all modules and logic in the IC.

May be used in addition to internally generated power on reset signal (logical AND, both internal and external signals are considered active low). |

| 17 | Power | GND | - | - | - |

| 18 | GPIO-SNVS | SNVS-TAMPER8 | SNVS_TAMPER8 | GPIO5_IO08 | Tamper input (SNVS power domain) or GPIO 3.3V. |

| 19 | USB | USB-OTG2-DP | USB_OTG2_DP | - | Leave open if not used. |

| 20 | Power | GND | - | - | - |

| 21 | USB | USB-OTG2-DN | USB_OTG2_DN | - | Leave open if not used. |

| 22 | Power | GND | - | - | - |

| 23 | Power | GND | - | - | - |

| 24 | GPIO-SNVS | SNVS-TAMPER7 | SNVS_TAMPER7 | GPIO5_IO07 | Tamper input (SNVS power domain) or GPIO 3.3V. |

| 25 | USB | USB-OTG1-DP | USB_OTG1_DP | - | Leave open if not used. |

| 26 | Power | GND | - | - | - |

| 27 | USB | USB-OTG1-DN | USB_OTG1_DN | - | Leave open if not used. |

| 28 | Power | GND | - | - | - |

| 29 | Power | GND | - | - | - |

| 30 | GPIO-SNVS | SNVS-TAMPER4 | SNVS_TAMPER4 | GPIO5_IO04 | Tamper input (SNVS power domain) or GPIO 3.3V. |

| 31 | USB | nUSB-OTG-CHD | USB_OTG1_CHD_B | - | Leave open if not used. |

| 32 | GPIO-SNVS | SNVS-TAMPER1 | SNVS_TAMPER1 | GPIO5_IO01 | Tamper input (SNVS power domain) or GPIO 3.3V. |

| 33 | JTAG | JTAG-MOD | JTAG_MOD | - | Leave open if not used. |

| 34 | GPIO-SNVS | SNVS-TAMPER3 | SNVS_TAMPER3 | GPIO5_IO03 | Tamper input (SNVS power domain) or GPIO 3.3V. |

| 35 | Power | GND | - | - | - |

| 36 | GPIO-SNVS | SNVS-TAMPER0 | SNVS_TAMPER0 | GPIO5_IO00 | Tamper input (SNVS power domain) or GPIO 3.3V. |

| 37 | CLK1-N | CCM_CLK1_N | - | General purpose differential high speed clock input/output.

Leave open if not used. | |

| 38 | Power | GND | - | - | - |

| 39 | CLK1-P | CCM_CLK1_P | - | General purpose differential high speed clock input/output.

Leave open if not used. | |

| 40 | Power | GND | - | - | - |

| 41 | Power | GND | - | - | - |

| 42 | GPIO-SNVS | SNVS-TAMPER6 | SNVS_TAMPER6 | GPIO5_IO06 | Tamper input (SNVS power domain) or GPIO 3.3V. |

| 43 | JTAG | JTAG-TDI | JTAG_TDI | - | JTAG TDI input line or GPIO. |

| 44 | GPIO-SNVS | SNVS-TAMPER2 | SNVS_TAMPER2 | GPIO5_IO02 | Tamper input (SNVS power domain) or GPIO 3.3V. |

| 45 | GPIO | GPIO-8 | GPIO1_IO08 | PWM1_OUT

WDOG1_WDOG_B SPDIF_OUT CSI_VSYNC USDHC2_VSELECT CCM_PMIC_RDY UART5_RTS_B |

Universal GPIO with 3.3V logic levels. |

| 46 | JTAG | JTAG-TMS | JTAG_TMS | - | JTAG TMS input line or GPIO. |

| 47 | GPIO | GPIO-4 | GPIO1_IO04 | ENET1_REF_CLK1

PWM3_OUT USB_OTG1_PWR USDHC1_RESET_B ENET2_1588_EVENT0_IN UART5_TX |

Universal GPIO with 3.3V logic levels. |

| 48 | JTAG | JTAG-nTRST | JTAG_TRST_B | - | JTAG TRST input line (active L) or GPIO. |

| 49 | GPIO | GPIO-5 | GPIO1_IO05 | ENET2_REF_CLK2

PWM4_OUT ANATOP_OTG2_ID CSI_FIELD USDHC1_VSELECT ENET2_1588_EVENT0_OUT UART5_RX |

Universal GPIO with 3.3V logic levels.

WLAN-ENABLE in SOM with WiFi/BT module |

| 50 | Power | GND | - | - | - |

| 51 | Power | GND | - | - | - |

| 52 | JTAG | JTAG-TDO | JTAG_TDO | - | JTAG TDO output line or GPIO. |

| 53 | GPIO | GPIO-7 | GPIO1_IO07 | ENET1_MDC

ENET2_MDC USB_OTG_HOST_MODE CSI_PIXCLK USDHC2_CD_BCCM_STOP UART1_RTS_B |

Universal GPIO with 3.3V logic levels. |

| 54 | JTAG | JTAG-TCK | JTAG_TCK | - | JTAG TCK input line or GPIO.

Connected to JTAG-TCK line (via separating resistor 10k). |

| 55 | GPIO | GPIO-3 | GPIO1_IO03 | I2C1_SDA

GPT1_COMPARE3 USB_OTG2_OC USDHC1_CD_B CCM_DI0_EXT_CLK SRC_TESTER_ACK |

Universal GPIO with 3.3V logic levels. |

| 56 | GPIO | GPIO-9 | GPIO1_IO09 | PWM2_OUT

WDOG1_WDOG_ANY SPDIF_IN CSI_HSYNC USDHC2_RESET_B USDHC1_RESET_B UART5_CTS_B |

Universal GPIO with 3.3V logic levels. |

| 57 | COM-GPIO | UART1-TXD | UART1_TX_DATA | ENET1_RDATA02

I2C3_SCL CSI_DATA02 GPT1_COMPARE1 GPIO1_IO16 SPDIF_OUT UART5_TX |

Default: UART1 TxD output or universal GPIO with 3.3V logic levels. |

| 58 | GPIO | GPIO-2 | GPIO1_IO02 | I2C1_SCL

GPT1_COMPARE2 USB_OTG2_PWR ENET1_REF_CLK_25M USDHC1_WPS DMA_EXT_EVENT00 SRC_ANY_PU_RESET UART1_TX |

Universal GPIO with 3.3V logic levels. |

| 59 | Power | GND | - | - | - |

| 60 | Power | GND | - | - | - |

| 61 | GPIO | GPIO-6 | GPIO1_IO06 | ENET1_MDIO

ENET2_MDIO USB_OTG_PWR_WAKE CSI_MCLK USDHC2_WPCCM_WAIT CCM_REF_EN_B UART1_CTS_B |

Universal GPIO with 3.3V logic levels. |

| 62 | GPIO | GPIO-1 | GPIO1_IO01 | I2C2_SDA

GPT1_COMPARE1 USB_OTG1_OC ENET2_REF_CLK2 MQS_LEFT ENET1_1588_EVENT0_OUT SRC_EARLY_RESET WDOG1_WDOG_B |

Universal GPIO with 3.3V logic levels. |

| 63 | COM-GPIO | UART1-RXD | UART1_RX_DATA | ENET1_RDATA03

I2C3_SDA CSI_DATA03 GPT1_CLK GPIO1_IO17 SPDIF_IN UART5_RX |

Default: UART1 RxD input or universal GPIO with 3.3V logic levels. |

| 64 | GPIO | GPIO-0 | GPIO1_IO00 | I2C2_SCL

GPT1_CAPTURE1 ANATOP_OTG1_ID ENET1_REF_CLK1 MQS_RIGHT ENET1_1588_EVENT0_IN SRC_SYSTEM_RESET WDOG3_WDOG_B |

Universal GPIO with 3.3V logic levels. |

| 65 | COM-GPIO | UART2-TXD | UART2_TX_DATA | ENET1_TDATA02

I2C4_SCL CSI_DATA06 GPT1_CAPTURE1 GPIO1_IO20 ECSPI3_SS0 |

Default: UART2 TxD output or universal GPIO with 3.3V logic levels. |

| 66 | COM-GPIO | UART1-CTS | UART1_CTS_B | ENET1_RX_CLK

USDHC1_WP CSI_DATA04 ENET2_1588_EVENT1_IN GPIO1_IO18 USDHC2_WP UART5_CTS_B |

Default: UART1 CTS output or universal GPIO with 3.3V logic levels. |

| 67 | COM-GPIO | UART2-RXD | UART2_RX_DATA | ENET1_TDATA03

I2C4_SDA CSI_DATA07 GPT1_CAPTURE2 GPIO1_IO21 SJC_DONE ECSPI3_SCLK |

Default: UART2 RxD input or universal GPIO with 3.3V logic levels. |

| 68 | COM-GPIO | UART5-RXD | UART5_RX_DATA | ENET2_COL

I2C2_SDA CSI_DATA15 CSU_CSU_INT_DEB GPIO1_IO31 ECSPI2_MISO EPDC_PWRCTRL03 |

Default: UART5 RxD input or universal GPIO with 3.3V logic levels. |

| 69 | COM-GPIO | UART3-TXD | UART3_TX_DATA | ENET2_RDATA02

CSI_DATA01 UART2_CTS_B GPIO1_IO24 SJC_JTAG_ACT |

Default: UART3 TxD input or universal GPIO with 3.3V logic levels. |

| 70 | Power | GND | - | - | - |

| 71 | Power | GND | - | - | - |

| 72 | COM-GPIO | UART2-CTS | UART2_CTS_B | ENET1_CRS

FLEXCAN2_TXCSI_DATA08 GPT1_COMPARE2 GPIO1_IO22 SJC_DE_B ECSPI3_MOSI |

Default: UART2 CTS output or universal GPIO with 3.3V logic levels. |

| 73 | COM-GPIO | UART3-RXD | UART3_RX_DATA | ENET2_RDATA03

CSI_DATA00 UART2_RTS_B GPIO1_IO25 EPIT1_OUT |

Default: UART3 RxD input or universal GPIO with 3.3V logic levels. |

| 74 | COM-GPIO | UART1-RTS | UART1_RTS_B | ENET1_TX_ER

USDHC1_CD_BCSI_DATA05 ENET2_1588_EVENT1_OUT GPIO1_IO19 USDHC2_CD_B UART5_RTS_B |

Default: UART1 RTS input or universal GPIO with 3.3V logic levels. |

| 75 | COM-GPIO | UART4-TXD | UART4_TX_DATA | ENET2_TDATA02

I2C1_SCL CSI_DATA12 CSU_CSU_ALARM_AUT02 GPIO1_IO28 ECSPI2_SCLK |

Default: UART4 TxD output or universal GPIO with 3.3V logic levels. |

| 76 | COM-GPIO | UART3-CTS | UART3_CTS_B | ENET2_RX_CLK

FLEXCAN1_TX CSI_DATA10 ENET1_1588_EVENT1_IN GPIO1_IO26 EPIT2_OUT |

Default: UART3 CTS output or universal GPIO with 3.3V logic levels. |

| 77 | COM-GPIO | UART4-RXD | UART4_RX_DATA | ENET2_TDATA03

I2C1_SDA CSI_DATA13 CSU_CSU_ALARM_AUT01 GPIO1_IO29 ECSPI2_SS0 EPDC_PWRCTRL01 |

Default: UART4 RxD input or universal GPIO with 3.3V logic levels. |

| 78 | COM-GPIO | UART2-RTS | UART2_RTS_B | ENET1_COL

FLEXCAN2_RX CSI_DATA09 GPT1_COMPARE3 GPIO1_IO23 SJC_FAIL ECSPI3_MISO |

Default: UART2 RTS input or universal GPIO with 3.3V logic levels. |

| 79 | COM-GPIO | UART5-TXD | UART5_TX_DATA | GPIO1_IO30

ECSPI2_MOSI EPDC_PWRCTRL02 ENET2_CRS I2C2_SCL CSI_DATA14 CSU_CSU_ALARM_AUT00 |

Default: UART5 TxD output or universal GPIO with 3.3V logic levels. |

| 80 | COM-GPIO | UART3-RTS | UART3_RTS_B | ENET2_TX_ER

FLEXCAN1_RX CSI_DATA11 ENET1_1588_EVENT1_OUT GPIO1_IO27 WDOG1_WDOG_B |

Default: UART3 RTS input or universal GPIO with 3.3V logic levels. |

| 81 | Power | GND | - | - | - |

| 82 | Power | GND | - | - | - |

| 83 | NC | - | - | - | - |

| 84 | Power | GND | - | - | - |

| 85 | Power | +3.3VOUT | - | - | +3.3V generated by SOM's LDO. |

| 86 | NC | - | - | - | - |

| 87 | Power | +3.3VOUT | - | - | +3.3V generated by SOM's LDO. |

| 88 | Power | +3.3VOUT | - | - | +3.3V generated by SOM's LDO. |

| 89 | Power | +3.3VOUT | - | - | +3.3V generated by SOM's LDO. |

| 90 | Power | +3.3VOUT | - | - | +3.3V generated by SOM's LDO. |

| 91 | Power | +3.3VOUT | - | - | +3.3V generated by SOM's LDO. |

| 92 | Power | +3.3VOUT | - | - | +3.3V generated by SOM's LDO. |

| 93 | Power | +3.3VOUT | - | - | +3.3V generated by SOM's LDO. |

| 94 | NC | - | - | - | - |

| 95 | NC | - | - | - | - |

| 96 | Power | +5VIN | - | - | +4.0-5.5V input power supply. |

| 97 | Ethernet | ENET1-RXD0 | ENET1_RX_DATA0 | UART4_RTS_B

PWM1_OUT CSI_DATA16 FLEXCAN1_TX GPIO2_IO00 KPP_ROW00 USDHC1_LCTL EPDC_SDCE04 |

Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. |

| 98 | Power | +5VIN | - | - | +4.0-5.5V input power supply. |

| 99 | Ethernet | ENET1-RXD1 | ENET1_RX_DATA1 | UART4_CTS_B

PWM2_OUT CSI_DATA17 FLEXCAN1_RX GPIO2_IO01 KPP_COL00 USDHC2_LCTL EPDC_SDCE05 |

Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. |

| 100 | Power | +5VIN | - | - | +4.0-5.5V input power supply. |

| 101 | Ethernet | ENET1-CRS-DV | ENET1_RX_EN | UART5_RTS_B

CSI_DATA18 FLEXCAN2_TX GPIO2_IO02 KPP_ROW01 USDHC1_VSELECT EPDC_SDCE06 |

Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. |

| 102 | Power | +5VIN | +4.0-5.5V input power supply. | ||

| 103 | Power | GND | - | - | - |

| 104 | Power | +5VIN | +4.0-5.5V input power supply. | ||

| 105 | Ethernet | ENET2-TX-CLK | ENET2_TX_CLK | UART8_CTS_B

ECSPI4_MISO ENET2_REF_CLK2 GPIO2_IO14 KPP_ROW07 ANATOP_OTG2_ID EPDC_SDDO14 |

Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels.

10R resistor connected in series. |

| 106 | Power | +5VIN | +4.0-5.5V input power supply. | ||

| 107 | Power | GND | - | - | - |

| 108 | Power | +5VIN | +4.0-5.5V input power supply. | ||

| 109 | Ethernet | ENET2-RXER | ENET2_RX_ER | UART8_RTS_B

ECSPI4_SS0 EIM_ADDR25 GPIO2_IO15 KPP_COL07 WDOG1_WDOG_ANY EPDC_SDDO15 |

Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels.

Connected to WDOG-B line. |

| 110 | Power | +5VIN | - | - | +4.0-5.5V input power supply. |

| 111 | Ethernet | ENET2-RXD0 | ENET2_RX_DATA0 | UART6_TX

I2C3_SCL ENET1_MDIO GPIO2_IO08 KPP_ROW04 USB_OTG1_PWR EPDC_SDDO08 |

Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. |

| 112 | Power | +5VIN | - | - | +4.0-5.5V input power supply. |

| 113 | Ethernet | ENET2-RXD1 | ENET2_RX_DATA1 | UART6_RX

I2C3_SDA ENET1_MDC GPIO2_IO09 KPP_COL04 USB_OTG1_OCE PDC_SDDO09 |

Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. |

| 114 | Ethernet | ENET1-TXEN | ENET1_TX_EN | UART6_RTS_B

PWM6_OUT CSI_DATA21 ENET2_MDC GPIO2_IO05 KPP_COL02 WDOG2_WDOG_RST_B_DEB EPDC_SDCE09 |

Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels. |

| 115 | Power | GND | - | - | - |

| 116 | Power | GND | - | - | - |

| 117 | Ethernet | ENET2-CRS-DV | ENET2_RX_EN | UART7_TX

I2C4_SCL EIM_ADDR26 GPIO2_IO10 KPP_ROW05 ENET1_REF_CLK_25M EPDC_SDDO10 |

Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. |

| 118 | Ethernet | ENET1-TX-CLK | ENET1_TX_CLK | UART7_CTS_B

PWM7_OUT CSI_DATA22 ENET1_REF_CLK1 GPIO2_IO06 KPP_ROW03 GPT1_CLK EPDC_SDOED |

Ethernet MAC1-PHY interface signal or universal GPIO with 3.3V logic levels.

10R resistor connected in series. |

| 119 | Ethernet | ENET2-TXD1 | ENET2_TX_DATA1 | UART8_TX

ECSPI4_SCLK EIM_EB_B03 GPIO2_IO12 KPP_ROW06 USB_OTG2_PWR EPDC_SDDO12 |

Ethernet MAC2-PHY interface signal or universal GPIO with 3.3V logic levels. |

| 120 | Power | GND | - | - | - |

| 121 | Ethernet | ENET2-TXEN | ENET2_TX_EN | UART8_RX

ECSPI4_MOSI EIM_ACLK_FREERUN GPIO2_IO13 KPP_COL06 USB_OTG2_OC EPDC_SDDO13 |

|

| 122 | Ethernet | ENET1-TXD0 | ENET1_TX_DATA0 | UART5_CTS_B